IT/ASIC | FPGA 2016. 9. 22.

edge detect pulse - 트리거된 이벤트를 알아내 한 클럭 pulse 만들기

머 제목부터 어렵다.정하기가..국어가... 왜 - 시나리오어떤 신호가 '1' 인 상태로 여러 클럭에 걸쳐져 있다.그런데 나는 '0' 에서 '1'로 올라간 이벤트를 알려주는 것처럼 한 번의 사건에 한 클럭만큼의 이벤트 펄스를 만들기를 원한다.해결은 그림으로이렇게 하면 된다. 즉 그림의 OUT 신호를 보고 사용하면 해결~~그림은 남이 그린 것이므로 원본글의 위치를 알려드립니다.보시고 HDL 코드도 필요하다고 생각하시면 해당글에 가셔서 꼭 읽어보세요. http://www.boldport.com/blog/2015/4/3/edge-detect-ad-nauseam 즐~~

IT/ASIC | FPGA 2016. 9. 22.

CDC(Clock Domain Crossing) 설계시 반드시 들어가는 synchronizer

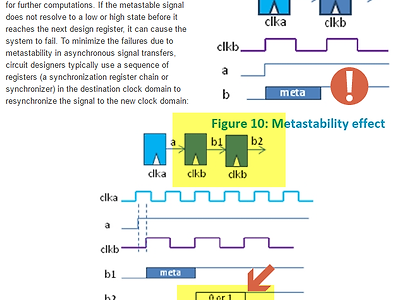

이전글에 이어 하나더, ASIC 설계시에 가장 중요한,실제 합성 후의 이상한 현상이 발생하는 경우 가장 많이 의심하는 이부분 CDC 설계에서 기본적인 것이라 볼 수 있다.그림으로 설명이 가능하다.물론 원본글은 아래 글에 방문하여 전체를 읽어 보는 것이 좋다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 무작정 다른 클럭의 시그널을 보고 사용하는 경우 Meta 상태의 값을 레퍼런스 할 수 있으므로이후 동작을 보장할 수 없다. 경우에 따라 다른 상황이 발생할 수도 있고, 잘 동작할 수도 있다. 운좋게.. 무튼, 그래서 무조건 F/F 2개 정도를 clock domain 사이에 넣어주는 것이 일반적인 기법..

IT/ASIC | FPGA 2016. 9. 22.

Recommended reset synchronization scheme

설계시 참고할 내용이 정말 많은 필수 페이지 일단 그중에서 필요한 내용은 바로 이것.원본글은 여기다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 이 그림이 뜻하는 바는 알고 가자. 리셋상태로 가는 것은 언제든지 async 한 조건으로 가고리셋에서 풀리는 경우에는 내부 시스템 클럭에 맞추어서 풀리도록 한다.여러 F/F 동작에 안정성을 부여할 수 있다. 즐