IT/ASIC | FPGA 2017. 5. 26.

인터뷰 예상 질문 - 반도체 설계 인력

이런 대단한 블로거가 있나? 반도체 설계자들이 인터뷰 준비를 위한 예상 질문리스트 (답변은 일부 있음) 정리해 놓은 글 발견세세히 다 알지는 못하지만 자기 분야에 맞는 글을 읽어보고 정리해 보면 쵝오~~Backend (Physical Design) Interview Questions and AnswersMar 12, 2008 ... Backend (Physical Design) Interview Questions and Answers. Below are the sequence of questions asked for a physical design engineer.asic-soc.blogspot.com/2008/.../backend-physical-design-interview.htmlCompanywis..

IT/ASIC | FPGA 2017. 5. 26.

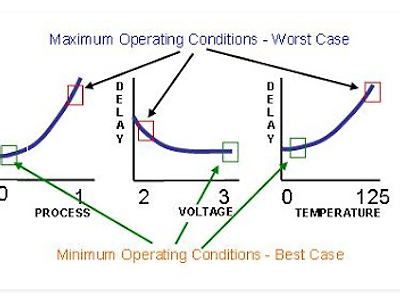

Temperature inversion

Temperature inversion – concept and phenomenon(http://vlsiuniverse.blogspot.kr/2015/04/temperature-inversion-deep-dive-into.html)머 공정이 낮아질수록 변수가 복잡해짐.단순히 온도가 낮고 높은 온도이면 best case 인데. 잘은 모르지만 공정이 낮아지면 원칙에서 벗어나 온도가 높아도 가끔 best case의 범위를 넘는 것들이 나오는 경우도 있음. 당연히 그 반대의 경우도 생각해야 하고...단어만으로 이해하면 이런 뜻이것 같은데. 머 틀려도 어쩔수 없지.시원한 바다가 생각나는 여름이~~출처: https://pixabay.com/en/santorini-oia-greece-water-1571484/

IT/ASIC | FPGA 2017. 5. 26.

Process-Voltage-Temperature (PVT) Variations and Static Timing Analysis

참고글 소개, 너무 기술적인 내용이라 읽기는 싫지만 가끔은 찾아봐야 함(http://asic-soc.blogspot.kr/2008/03/process-variations-and-static-timing.html)Sources of variation can be:Process variation (P)Supply voltage (V)Operating Temperature (T)The best and worst design corners are defined as follows:Best case: fast process, highest voltage and lowest temperature 빠른 공정, 높은 전압, 낮은 온도Worst case: slow process, lowest voltage and hig..