Verilog 를 사용하는 할당 구문은 크게 =, <= 2개를 많이 사용하는데 헷갈릴까봐 일단 정리

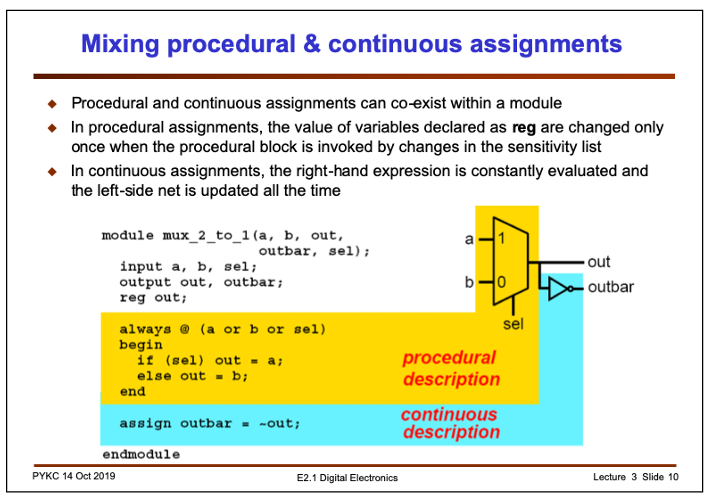

Continuous Assigns

assign a = b & c;

혹은 딜레이 요소를 넣어서 (물론 딜레이는 합성이 되지 않는다)

assign #10 a = b & c;

Procedural Assignment

always 문이나 initial 문 안에서 사용되는 할당 문이다.

일단 2가지가 있다. blocking, non-blocking 일단 머 하드웨어의 기본은 non-blocking 이다.

C 코드가 아니므로, 순차적 실행은 존재할 수 없다.

blocking 은 대부분 그냥 combinational 회로로 대체되고, non-blocking 은 F/F, Latch 가 사용된다고 보면 된다.

A procedural assignment updates the value of register data types.

Syntax:

[ delay ] register_name = [ delay ] expression; // blocking

[ delay ] register_name <= [ delay ] expression; // non-blocking

always @(a or b or c or d)

y = (a | b) & (~c ^ d);

always @* begin

y = (a | b) & (~c ^ d);

z = (e | f) & (~g ^ h);

end예제

https://www.hdlworks.com/hdl_corner/verilog_ref/items/ProceduralAssignment.htm

https://verilogams.com/refman/modules/discrete-processes.html

begin

a = 0;

#10 a = 1;

#5 a = 2;

end // time 0: a=0; time 10: a=1; time 15 (#10+#5): a=2;

begin

a <= 0;

#10 a <= 1;

#5 a <= 2;

end // time 0: a=0; time 5: a=2; time 10: a=1;

begin

a <= b;

b <= a;

end // both assignments are evaluated before a or b changes주의할 점

assign (좌변) = (우변) ; 꼴로 작성을 하게 되는데 좌변에는 항상 wire type 변수만이 올 수가 있습니다.

reg는 assign 문의 우변에는 올 수 있지만 좌변에 올 수 없습니다.

'IT > ASIC | FPGA' 카테고리의 다른 글

| Verilog - 파이썬으로 테스트 벤치 작성하기 cocotb - 킵 (0) | 2024.02.15 |

|---|---|

| Verilog - RGMII 샘플 코드 - 북마크 (0) | 2024.02.15 |

| Verilog 기초 - case 문 (0) | 2024.02.15 |

| Xilinx Vivado - 다운로드 및 설치 (1) | 2024.02.13 |

| Verilog - flatten array - 2차원 배열 1차원으로 변환 (1) | 2024.02.05 |