Verilog 로 구현된 RGMII 코드가 있어서 일단 공유한다. RGMII 는 이데넷 PHY칩과 MAC 사이의 통신 방법이라고 보면 된다.

일단 아래 블로그글을 참고하자.

https://www.circuitden.com/blog/23

CircuitDen | Artin Isagholian

This article is for hardcore digital design wizards who don’t want to use any intermediate processors (kiss your software team goodbye) or proprietary IPs to communicate with their FPGAs via an ethernet connection. All you need is a PC, FPGA, and an ethe

www.circuitden.com

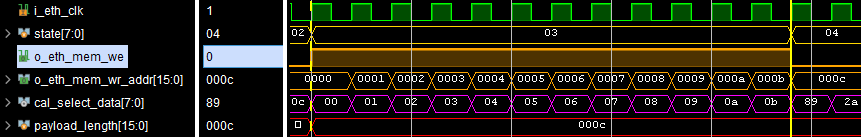

RGMII 코드

코드는 GitHub 에 공유되어 있다. 공유하고 공부꺼리를 남겨주는 이들이 놀랍다.

https://github.com/0xArt/RGMII_Ethernet_Transceiver_Verilog

GitHub - 0xArt/RGMII_Ethernet_Transceiver_Verilog: Verilog module to transmit/receive to/from RGMII compatible ethernet PHY

Verilog module to transmit/receive to/from RGMII compatible ethernet PHY - 0xArt/RGMII_Ethernet_Transceiver_Verilog

github.com

자세한 내용은 저자 블로그글을 참고하는 것이 좋겠죠

'IT > ASIC | FPGA' 카테고리의 다른 글

| Xilinx - Vivado RAM 초기화 값 입력 - coe 파일 (0) | 2024.02.15 |

|---|---|

| Verilog - 파이썬으로 테스트 벤치 작성하기 cocotb - 킵 (0) | 2024.02.15 |

| Verilog - Assignment 할당 구문 - blocking, non-blocking (0) | 2024.02.15 |

| Verilog 기초 - case 문 (0) | 2024.02.15 |

| Xilinx Vivado - 다운로드 및 설치 (1) | 2024.02.13 |