ASIC, FPGA 설계시에 CDC clock domain crossing 내용을 알고 있는지 물어보는 사람이 많은 것 같네요. 제가 알고 있는 방법이 너무 간단해서 이게 꼭 공고에 나올만한 내용인지 모르겠지만 (내가 모르는 무엇인가가 엄청 있는건가요? ^^;;;;)

결론적으로, 클럭이 다른 도메인 사이의 시그널 교환에서는 반드시 무조건 필수적으로

metastable 상태가 전달 되지 않도록 Multi-stage synchronizer 를 사용하면 해결된다는 것!!

참고한 글은 유명한 블로그 님들의 글입니다.

https://secondspot.tistory.com/18 <- 강추 들어가서 연구하세요 :)

http://babyworm.net/archives/150

Metastable 상태

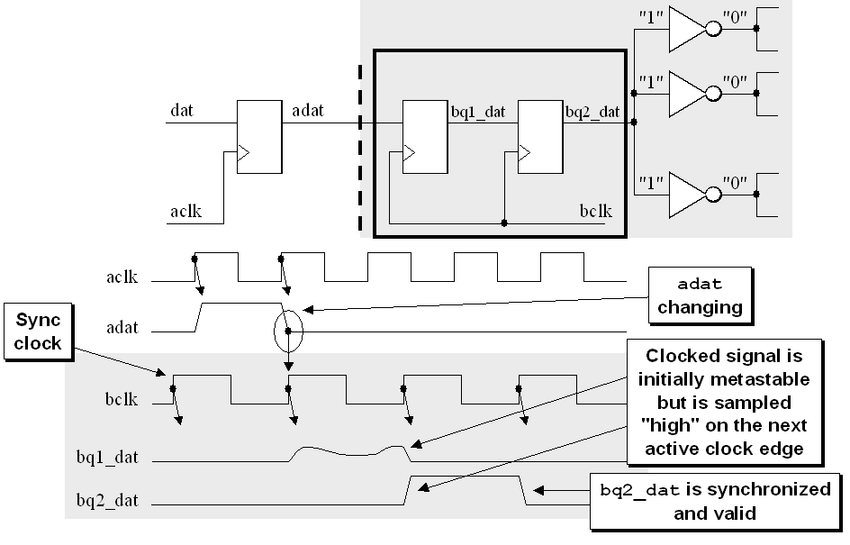

아래 그림처럼, 파형도의 전달 시그널이 찌그려져 있는 것이 metastable 상태라고 생각하면 됩니다. (제가 알기론..틀렸으면 구루님들이 알려주세요)

2개의 플립 플롭을 이용해서 시그널을 사용하는 모듈에서 전달 받으면 metastable 상태가 전달되지 않으니 무조건 이렇게 구현해서 써야 합니다!!!!

추가 주의 사항에 대한 글도 있다. 아래 블로그 글에 보면 전반적인 내용이 전체로 소개가 잘 되어 있다. 바이블처럼 들어가서 보자.

첫번 째로는 Clock1 Domain에서 Clock2 Domain으로 전달되는 신호는 중간에 Combination Logic 없이 Register의 출력 값이어야 한다.

두 번째로는 Clock1 Domain과 Clock2 Domain 간의 Frequency와 CDC boundary를 고려해야 한다.

출처: https://secondspot.tistory.com/18 [소소하게 일상을 기록하는 페이지:티스토리]

'IT > ASIC | FPGA' 카테고리의 다른 글

| Verilog - 숫자 표현 정리 - Signed vector 내용 중요 (0) | 2024.02.20 |

|---|---|

| Xilinx Vivado - SPRAM, DPRAM, block RAM 활용 (1) | 2024.02.20 |

| Verilog - 합성에 유리한 coding 스타일 (2) | 2024.02.16 |

| Verilog - 곱셈이 합성이 되나요? (1) | 2024.02.16 |

| Xilinx - Vivado RAM 초기화 값 입력 - coe 파일 (0) | 2024.02.15 |