IT/ASIC | FPGA 2024. 4. 30.

AXI 프로토콜 테스트 환경 설계 1 - 인터페이스 모델 정의

주의!!! 코드는 아직 검증되기 전입니다. 전체적인 구조를 잡기 위해 올려두는 부분이니 그대로 활용이 불가합니다. AXI (Advanced eXtensible Interface) 버스는 ARM이 설계한 고성능, 고대역폭의 시스템 온 칩(SoC) 버스 인터페이스입니다. AXI는 AMBA (Advanced Microcontroller Bus Architecture) 사양의 일부로서, 특히 대용량 데이터 처리와 복잡한 시스템 설계에 적합한 인터페이스를 제공합니다. 이제 AXI의 주요 구성 요소와 특징을 자세히 설명해 드리겠습니다.AXI 인터페이스 주요 특징성능: 다중 마스터 및 슬레이브 구성을 지원하여 고성능 멀티프로세서 시스템 설계에 적합합니다.확장성: 모듈식 설계를 통해 다양한 구성 요소와의 효과적인 통합..

IT/ASIC | FPGA 2024. 2. 13.

Xilinx Vivado - 다운로드 및 설치

FPGA 에 프로그래밍 할 수 있는 툴인 Vivado를 다운로드 하고 설치해 보자. 사용자 계정 생성 우선 툴 제공 업체인 AMD 사이트에서 계정을 먼자 만들고 로그인 해야 한다. 계정 생성하는 방법은 AMD 사이트에서 로그인 버튼은 누르면, 아래와 같이 생성할 수 있는 "계정 만들기" 버튼을 볼 수 있다. 클릭해서 생성작업을 해보자. 정보를 입력하고 생성이 완료되면, 꼭 로그인을 하도록 한다. Vivado Download 이제 Vivado 툴을 다운로드 하면 된다. 해당 툴을 다운로드 하는 경로는 아래와 같다. 다운로드 주소https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tool..

IT/ASIC | FPGA 2018. 11. 28.

(2018)[IDEC 연구원 교육] Cell-Based 설계 Flow 교육

(2018)[IDEC 연구원 교육] Cell-Based 설계 Flow 교육 그리고, IDEC 의 강의 리스트에도 이 자료의 소개가 있다. (2018)[IDEC 연구원교육] Cell-based flow 교육 - http://www.idec.or.kr/vod/apply/view/?&no=144 [강좌 개요] - 디지털 칩 설계 전체 과정 중, 본 과정은 Front – End 과정을 다루는데 초심자의 눈높이에 맞추어 이론과 실습을 진행함. 기존의 Front-End 강좌에 Verdi Verification과정을 추가하여 새롭게 업데이트 했습니다 - IC Compiler 를 이용한 Layout 방법을 소개하고 Back-end 과정 진행 시 주의 사항에 대해서 학습할 수 있도록 합니다. [사전지식] 디지털 논리회로..

IT/ASIC | FPGA 2018. 11. 16.

Xilinx 제품군 선택은 어떻게

Xilinx 제품군 선택은 어떻게?? 너무 많이 있고 고르기 힘들다. 무조건 EVB 많고 레퍼런스 많은 것을 써야 한다. 대새를 따라야지..무튼, Xilinx 홈에 있는 Selection guide 를 저장해 둔다. 7 Series Product Tables and Product Selection Guide Spartan-7, Artix-7, Kintex-7, Virtex-7 등 7 시리즈들의 간단한 특징과 선택가이드가 나와 있다.ㅋㅋ 왼쪽에서 오른쪽으로 갈 수록 가격이 비싼 순서인듯~~비싼게 좋은 거여!! Zynq-7000 AP SoC Family Product Tables and Product Selection Guide 오호 요건 ARM Cortex-A9 이 내부에 떡 박혀있는 FPGA 시리즈PL(..

IT/ASIC | FPGA 2017. 6. 30.

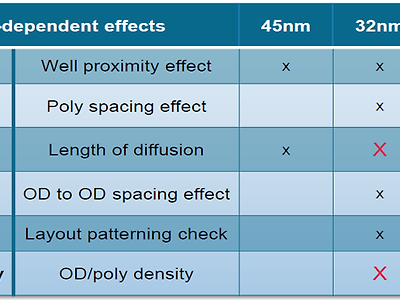

PV - Physical verification / DRC, LVS, ERC, DFM

PV - Physical verification / DRC, LVS, ERC, DFM개발 보단 검증의 시대.검증이라는 것은 끝이 없는 터.. 어느 정도 기준을 세워서 그만 할 수 있어야 하는 용기가 필요..참고: https://www.synopsys.com/news/pubs/compiler/artlead_design-sep05.html?cmp=NLC-compiler&Link=Sep05_Issue_Art1무튼..용어들을 살펴보자.DRC - Design Rule Check기본적으로 파운드리가 제공하는 룰이 있다. 그 룰에 위배 되는지 아닌지 판단하면 된다.Consists of dimensional rules (width/spacing/coverage landing) for metals, diffusion, ..

IT/ASIC | FPGA 2017. 6. 23.

[용어] Transistor Level Description

[용어] Transistor Level Description머 거창한 얘기는 아니고, 이렇게 기술하기 위해서 많이 들리는 단어들이 있다. 1. SPICE (Simulation Program with Integrated Circuit Emphasis)- 디바이스 기술, 텍스트로..- Resistors, Inductor, Capacitor, Diode, MOS transistor- Sources-- Voltage and Current Sources--- V1 DC=5V, I1 AC=5mA,...-- Transient sources--- Pulse Source 파형형태, Piecewise Linear(PWL) 계단같은 형태의 단계형 파형..2. CDL (Circuit Description Language)- ..

IT/ASIC | FPGA 2017. 5. 26.

Temperature inversion

Temperature inversion – concept and phenomenon(http://vlsiuniverse.blogspot.kr/2015/04/temperature-inversion-deep-dive-into.html)머 공정이 낮아질수록 변수가 복잡해짐.단순히 온도가 낮고 높은 온도이면 best case 인데. 잘은 모르지만 공정이 낮아지면 원칙에서 벗어나 온도가 높아도 가끔 best case의 범위를 넘는 것들이 나오는 경우도 있음. 당연히 그 반대의 경우도 생각해야 하고...단어만으로 이해하면 이런 뜻이것 같은데. 머 틀려도 어쩔수 없지.시원한 바다가 생각나는 여름이~~출처: https://pixabay.com/en/santorini-oia-greece-water-1571484/

IT/ASIC | FPGA 2017. 5. 26.

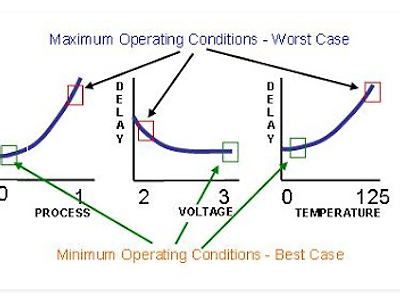

Process-Voltage-Temperature (PVT) Variations and Static Timing Analysis

참고글 소개, 너무 기술적인 내용이라 읽기는 싫지만 가끔은 찾아봐야 함(http://asic-soc.blogspot.kr/2008/03/process-variations-and-static-timing.html)Sources of variation can be:Process variation (P)Supply voltage (V)Operating Temperature (T)The best and worst design corners are defined as follows:Best case: fast process, highest voltage and lowest temperature 빠른 공정, 높은 전압, 낮은 온도Worst case: slow process, lowest voltage and hig..

IT/ASIC | FPGA 2017. 3. 31.

[기초] What is Tape out?

What is Tape-out ? 반도체 설계를 하다보면, Tape out 이라는 용어를 접하게 된다. 머 쉽게. 최종 결과물을 공장으로 내보내는 것을 말한다고 보면 된다. 이후에는 마스크를 실제 제작하게 되므로, 수정이 필요한 경우에 많은 비용을 감수해야 한다. 고로, Tape-out 이전에 꼭 잘 검증해야 한다는 것.. 어디선가는 PG 라고도 하는데 이는 Pattern Generation 의 약자로 같은 의미로 보면 된다. 근데 왜 tape out 인가? from : http://egloos.zum.com/analogwise/v/951048 이제, 설계한 제품을 마치고 공장으로 보내는 과정이 tape out이다. 일전에는 정말도 tape를 들고 뛰었다. 학교에서 공부할 때의 초창기에는 reel tap..

IT/ASIC | FPGA 2016. 9. 22.

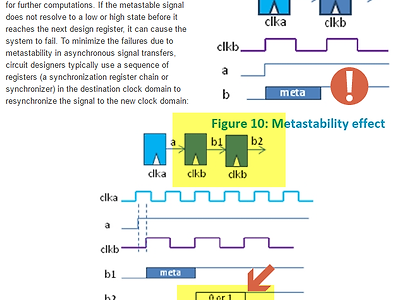

CDC(Clock Domain Crossing) 설계시 반드시 들어가는 synchronizer

이전글에 이어 하나더, ASIC 설계시에 가장 중요한,실제 합성 후의 이상한 현상이 발생하는 경우 가장 많이 의심하는 이부분 CDC 설계에서 기본적인 것이라 볼 수 있다.그림으로 설명이 가능하다.물론 원본글은 아래 글에 방문하여 전체를 읽어 보는 것이 좋다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 무작정 다른 클럭의 시그널을 보고 사용하는 경우 Meta 상태의 값을 레퍼런스 할 수 있으므로이후 동작을 보장할 수 없다. 경우에 따라 다른 상황이 발생할 수도 있고, 잘 동작할 수도 있다. 운좋게.. 무튼, 그래서 무조건 F/F 2개 정도를 clock domain 사이에 넣어주는 것이 일반적인 기법..