IT/ASIC | FPGA 2018. 11. 16.

Xilinx 제품군 선택은 어떻게

Xilinx 제품군 선택은 어떻게?? 너무 많이 있고 고르기 힘들다. 무조건 EVB 많고 레퍼런스 많은 것을 써야 한다. 대새를 따라야지..무튼, Xilinx 홈에 있는 Selection guide 를 저장해 둔다. 7 Series Product Tables and Product Selection Guide Spartan-7, Artix-7, Kintex-7, Virtex-7 등 7 시리즈들의 간단한 특징과 선택가이드가 나와 있다.ㅋㅋ 왼쪽에서 오른쪽으로 갈 수록 가격이 비싼 순서인듯~~비싼게 좋은 거여!! Zynq-7000 AP SoC Family Product Tables and Product Selection Guide 오호 요건 ARM Cortex-A9 이 내부에 떡 박혀있는 FPGA 시리즈PL(..

IT/ASIC | FPGA 2018. 10. 25.

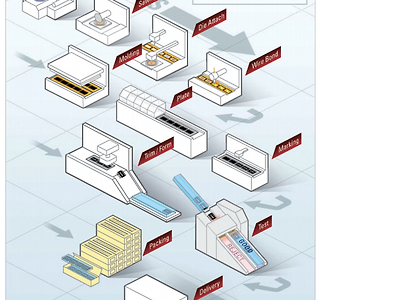

반도체 패키징 공정

반도체 패키징 공정을 대략적으로 살펴보면 다음과 같다. ① Back Grinding 공정 : 전공정에서 가공된 웨이퍼의 후면을 얇게 갈아내는 공정 ② Sawing(Dicing) 공정 : 웨이퍼를 개별 단위(net die)로 잘라내는 공정 ③ Die Attaching 공정 : 회로기판(substrate)에 칩을 붙여 고정하는 공정 ④ Wire Bonding : Gold Wire로 칩을 전기적으로 연결하는 공정 ⑤ Molding : EMC 물질로 칩이 실장된 기판을 감싸는 공정 ⑥ Marking : 레이저로 개별 제품에 제품 정보를 새기는 공정 ⑦ Solder Ball Mount : 회로기판에 솔더 볼을 붙여 아웃단자를 만드는 공정 ⑧ PKG Sawing : 모듈/보드/카드에 실장하도록 개별 반도체로 잘라내..

IT/ASIC | FPGA 2018. 10. 24.

반도체 전시회 - SEDEX Korea 2018

SEDEX Korea 2018간단한 전시회 참관후기 입니다. 맨 하단부에 Faraday 솔루션을 보기위해 참관했으나 거의 1/2 이상의 솔루션들이 공장자동화/산업용 필드버스 제품들이 놓여 있어 같이 살펴보고 왔습니다.RS Automation의 산업용 I/O 모듈로 EtherCAT 기반의 I/O 모듈 제품으로 국내 생산 제품입니다.하지만, 전체 제품을 자체 개발한 것은 아니고, 아래 그림의 Master Card 시리즈인 EtherCAT Controller 의 경우, NetX 솔루션을 그대로 도입해서 제품화된 것 같네요.BANNER 라는 독일 업체의 솔루션입니다.사진에서 보는 바와 같이 다양한 필드버스를 동시에 지원하고 있습니다.PROFI-NET, Modbus, Ethernet/IP, CANopen, Eth..

IT/ASIC | FPGA 2018. 10. 11.

Free Cortex-M processors for Xilinx FPGAs

Free Cortex-M processors for Xilinx FPGAs 블로그 기사 제목은 바로"Arm expands design possibilities with free Cortex-M processors for Xilinx FPGAs"https://www.arm.com/company/news/2018/10/arm-expands-design-possibilities-with-free-cortex-m-processors-for-xilinx-fpgas FPGA 시장이 점점 커질 것을 예상하고, arm에서 선제적으로 FPGA용 CortexM 시리즈를 무료로 배포한다.장점이야 링크 글에 있는 내용을 가져오면 머 당연한 말들이 적혀있다.Cortex-M1 이 원래 FPGA용 코어로 제공되고 있는 것으로 알고..

IT/ASIC | FPGA 2018. 10. 4.

Triple-Speed Ethernet Intel® FPGA IP Core

Triple-Speed Ethernet Intel® FPGA IP CoreThe Triple-Speed Ethernet Intel® FPGA IP core consists of a 10/100/1000 Mbps Ethernet media access control (MAC) and physical coding sublayer (PCS) intellectual property (IP). This IP function enables Intel FPGAs to interface to an external Ethernet PHY device, which interfaces to the Ethernet network.https://www.intel.com/content/www/us/en/programmable/p..

IT/ASIC | FPGA 2017. 8. 7.

Timing sign-off corner

Timing sign-off cornerLet us say, each minima/maxima in cell characteristics as ‘PVT corner’ and net characteristics as ‘extraction corner’. Each combination of PVT extraction corners is referred to as a ‘timing corner’ as it represents a point where timing will be extreme. http://vlsiuniverse.blogspot.kr/2014/01/timing-corners-dimensions-in-timing.html

IT/ASIC | FPGA 2017. 7. 18.

ASIC, SoC, 반도체, 설계 관련 글 모음

ASIC, SoC, 반도체, 설계 관련 글 모음 여러군데, 혹은 여기에 단편적으로 적어두다 보니 목차같은 페이지가 없다. 좀 정리가 안되더라도 한 페이지에 모아서 저장해 두면 좋겠다 생각하던 차에 Github pages 를 이용하여 jekyll 블로그를 하나 만들어서 해당 페이지를 만들어 두었다. 업데이트 열심히 해야지 ASIC, SoC, 반도체, 설계 관련 글 모음 (http://devbj.com/asic/) ASIC ASIC Design Tutorials - 위키사이트, 전체흐름을 살펴보자. 설계, FPGA, 검증. HDL 설계에 사용되는 hdl 언어(VHDL, Verilog, SystemVerilog, …) 관련 자료를 모아두자. Verilog http://www.testbench.in/ - 테스트..

IT/ASIC | FPGA 2017. 6. 30.

PV - Physical verification / DRC, LVS, ERC, DFM

PV - Physical verification / DRC, LVS, ERC, DFM개발 보단 검증의 시대.검증이라는 것은 끝이 없는 터.. 어느 정도 기준을 세워서 그만 할 수 있어야 하는 용기가 필요..참고: https://www.synopsys.com/news/pubs/compiler/artlead_design-sep05.html?cmp=NLC-compiler&Link=Sep05_Issue_Art1무튼..용어들을 살펴보자.DRC - Design Rule Check기본적으로 파운드리가 제공하는 룰이 있다. 그 룰에 위배 되는지 아닌지 판단하면 된다.Consists of dimensional rules (width/spacing/coverage landing) for metals, diffusion, ..

IT/ASIC | FPGA 2017. 6. 30.

실리콘 순도 표시 - 6N, 11N

실리콘 순도 표시.이런것이 있다네..순금은 보통 99.99% 면 충분한디..이놈의 반도체는 너무 결벽증이댜..99.999999% 정도 되야 태양전지에 쓰이고,99.99999999999% 이 정도는 되어야 반도체 공정에 사용할 수 있다냐..그런디 이걸 부르는 방법은 9의 소수점 이하 갯수로 부른다네. 즉 99.999999% 은 6N (six nine), 99.99999999999% 은 11N (eleven nine) 이렇게.출처: http://blog.daum.net/dasomcap/894from - https://pixabay.com/en/cockle-shell-coarse-grained-sand-571905/

IT/ASIC | FPGA 2017. 6. 23.

[용어] Transistor Level Description

[용어] Transistor Level Description머 거창한 얘기는 아니고, 이렇게 기술하기 위해서 많이 들리는 단어들이 있다. 1. SPICE (Simulation Program with Integrated Circuit Emphasis)- 디바이스 기술, 텍스트로..- Resistors, Inductor, Capacitor, Diode, MOS transistor- Sources-- Voltage and Current Sources--- V1 DC=5V, I1 AC=5mA,...-- Transient sources--- Pulse Source 파형형태, Piecewise Linear(PWL) 계단같은 형태의 단계형 파형..2. CDL (Circuit Description Language)- ..

IT/ASIC | FPGA 2017. 6. 2.

[스크랩] Chip size 관련 용어 - chip size, seal ring, scribe lane

원본글 : Chip size 관련 용어 - chip size, seal ring, scribe lane (http://blog.naver.com/beahey/90174222003) Chip Size 와 관련된 용어들 (chip size, seal ring, scribe lane) Chip Size 와 관련된 용어들 Keyword : chip size, seal ring, scribe lane Layout for core... blog.naver.com 그림은 원본글에 가셔서 보시도록 하시고, 필요한 것만 정리해 보면, Core logic 의 layout 결과물 + Seal ring 까지는 하나의 GDS 로 보통 만들어 진다. 이때 칩사이즈는, Scribe lane 을 포함할 수도 안할 수도 있다. 표기할..

IT/ASIC | FPGA 2017. 6. 2.

[Tool] Mentor Graphics - Calibre PERC (ESD check)

Mentor Graphics - Calibre PERC 뉴스레터의 내용인데, ㅋㅋ 어렵네~http://www.mentorkr.com/company/news20100113.htmlCalibre PERC 제품은 회로의 정전기 방전(ESD) 이벤트 보호 수준이 충분한지 확인하고 디자이너가 혼성신호 IC의 여러 파워 서플라이 간에 잘못된 연결이 있는지 손쉽게 확인할 수 있도록 하는 것을 비롯하여다양한 애플리케이션을 다룬다. Calibre PERC 제품은 ESD 검증 영역에서 제조 시 디바이스의 심각한결함을 유발하고 선적 및 어셈블리 과정에 디바이스가 쉽게 손상되도록 하고 현장에서 디바이스의 수명을떨어뜨리는 ESD 이벤트로부터 디바이스를 보호하는 데 필요한 회로의 완벽성을 확인한다. 또한 CalibrePERC 제..