IT/ASIC | FPGA 2024. 2. 15.

Verilog 기초 - case 문

Verilog 기초 문법과 관련된 것도 하나씩 정리해 보자. 오늘은 case 문이다. if 문과는 다르게 병력적으로 우선순위 없이 생긴다는 장점이 있다. 반드시 우선순위가 필요하다면 if else 문을 사용해야 하며, 같은 조건에서 mux 하는 로직 같은 경우에는 case 문을 활용하면 된다. 아래 문법과 예제는 다음 사이트에서 참고하였다. https://vlsiverify.com/verilog/case-statement/ Case 문법 기본 문법은 다음과 같다. case() : : : : begin ... ... end default: endcase 사실 예제로 보는 게 가장 낫다. Case 예제 module case_example; reg [2:0] data; always @(data) begin c..

IT/ASIC | FPGA 2024. 2. 13.

Xilinx Vivado - 다운로드 및 설치

FPGA 에 프로그래밍 할 수 있는 툴인 Vivado를 다운로드 하고 설치해 보자. 사용자 계정 생성 우선 툴 제공 업체인 AMD 사이트에서 계정을 먼자 만들고 로그인 해야 한다. 계정 생성하는 방법은 AMD 사이트에서 로그인 버튼은 누르면, 아래와 같이 생성할 수 있는 "계정 만들기" 버튼을 볼 수 있다. 클릭해서 생성작업을 해보자. 정보를 입력하고 생성이 완료되면, 꼭 로그인을 하도록 한다. Vivado Download 이제 Vivado 툴을 다운로드 하면 된다. 해당 툴을 다운로드 하는 경로는 아래와 같다. 다운로드 주소https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tool..

IT/ASIC | FPGA 2024. 2. 5.

Verilog - flatten array - 2차원 배열 1차원으로 변환

Verilog 에서 포트로 넘길때 2차원 배열이 되지 않는다는 슬픈 진실이 있네 ㅜㅜ 일단 보통 합성할 때 합성툴에서 다 자동으로 해줄 듯 한데 이를 손으로 해야 한다니 일단 방법은 알아두자고 https://stackoverflow.com/questions/28623819/how-to-flatten-array-in-verilog How to flatten array in Verilog As Verilog does not allow to pass the array as input to module, so how can we flatten any array in Verilog. Suppose I have this array: parameter [31:0] A [0:31]; wire [31:0] B I wan..

IT/ASIC | FPGA 2024. 2. 2.

Xilinx Vivado - FPGA 에 bit 생성해서 올리기 - 보드 테스트

Xilinx Vivado로 만들어지 bit 파일을 이제 실제 FPGA 에 올려서 보드 테스트를 해보자. 이과정도 툴 마다 달라서 일단 정리해 둔다. 먼저 여러 단계를 각각 누르지 말고, "Generate Bitstream" 을 그냥 확 누른다. 즉, 합성, P&R, 구현 다 한꺼번에 수행한다. 코드가 변경되어서 합성부터 구현까지 다시 하겠다는 창이다. 그냥 "Yes" 누르면 진행된다. 얼마나 빨리 하려고 이런걸 묻나 그냥 기본값을 4를 두고 오케이 본격적으로 합성을 수행하고 있음을 알수 있다. "Project Summary" 창에서 보면 현재 진행되는 과정을 볼 수 있다. 에러가 없다는 아래 메시지 창이 등장한다. 이제 다했으니 머할까요? 이런 창이다. FPGA에 bit를 올리기 위해 "Open Hard..

IT/ASIC | FPGA 2024. 2. 2.

Xilinx Vivado - 핀 할당 하기 Constraints 추가

Xilinx Vivado에서 원하는 핀을 할당 하려면 Constraints 파일을 추가해야 한다. 아니면 랜덤으로 막 핀을 Assign 하므로 하드웨어설계도와 맞출 필요가 있다. 참고로, FPGA하드웨어 핀을 선택하기 위해서는 기본적으로 어떤 핀을 뽑아야 할지 처음에는 랜덤으로 돌린 후에 하드웨어 설계를 진행하는 경우가 일반적이다. 아무튼 핀 할당을 해보자. 위의 그림처럼 수정하기를 눌러본다. 새로 만드는 것이므로 과감하게 "Create File"을 누른다. 나타나는 창에 원하는 이름만 딱 쓰고, OK 하면 그럼 다음과 같이 파일이 하나 생성됨을 볼 수 있다. 그럼 왼쪽 트리창에 하나 추가되어 있는데, 아시다시피 빈파일이다. 전구 모양 버튼 "Language Template" 을 누르면 기본 문법 구문을..

IT/ASIC | FPGA 2024. 2. 2.

Xilinx Vivado - FIFO Generator 로 사용자 FIFO 만들기

Xilinx Vivado 툴에서 제공되는 FIFO Generator 로 사용자 FIFO 만들기를 그냥 한번 해보고, 그림을 남겨둔다. FPGA는 참 어찌보면 쉽다. 이렇게 마법사로 FIFO를 원하는 대로 만들어 낼 수 있다니 8비트 UART 송수신용 FIFO가 필요해서 일단 IP 검색에서 FIFO Generator 를 선택하면 더블 클릭하거나 엔터를 치면 아래와 같은 창이 나타난다. 일단, 아무것도 하지 말고 자기가 원하는 이름만 변경하자. 이제 원하는 데이터 비트를 8비트로 변경해 보자. 위의 그림에서 "Native Ports" 라는 부분을 클릭하면, 아래 창이 나타난다. 아무것도 건드리지 말고 Data Port 만 수정하자. Width 를 8 로 변경하고 Tab을 누르면 아래 Read Width도 자..

IT/ASIC | FPGA 2024. 1. 25.

Xilinx JTAG – HS2, HS3, Platform Cable USB II

Xilinx JTAG 케이블 종류가 많은데 숫자가 보통 높은걸로 선택하는데 이것은 JTAG HS2 가 호환성이 더 좋은듯 Digilent FPGA 보드를 많이 쓰니, 해당 회사에서 만든 제품으로 알아보자!! https://digilent.com/reference/programmers/jtag-hs2/reference-manual?_ga=2.209894997.1913691520.1700123539-2102363698.1698815413#supported_target_devices Is JTAG-HS2 is compatible with Artix 7 series FPGA? @vertika.s, Yes, it is compatible. You can view the full supported Artix 7 시..

IT/ASIC | FPGA 2019. 11. 18.

불량분석 (Failure Analysis) EOS Test, I-V Curve - 반도체 테스트

FA, EOS Test, I-V Curve, 불량분석(Failure Analysis) - 반도체 테스트 물건을 팔면 다가 아니다. 여기저기 시장에서 불량이라고 분석을 요구하는 곳이 엄청나게 많다. 일일이 다 대응해 줄 수 있는 것은 아니지만, 리포트를 요구하는 업체들이 있으면 상당히 곤란하다. 중소기업의 경우, 어쩔 수 없이 외부 업체에 의뢰를 맡길 수 밖에 없다. 아래에 소개된 Microchip의 경우를 보면 이 과정을 위해 Lab을 따로 마련하고 있어, 과정이 표준화 되어 있고 대응일정이 비교적 명확하다. (부러움 ^^;;;) 무튼, 대부분의 문제를 EOS 문제로 생각하고 대응하게 되는데, 테스트 (Electrical Overstress)는 반도체 부품, 회로에 초과된 전자기적 신호 및 과전압에 의해..

IT/ASIC | FPGA 2019. 11. 18.

정전기 방전 손상모델및 시험방법 - ESD 반도체 테스트 자료

구글 검색 후 기술자료 모음 정전기 방전 손상모델및 시험방법정전기 방전 손상모델및 시험방법 - ESD 반도체 테스트 자료 전파기술원 2011.03 뉴스레터 자료 중 발췌된 내용 LG전자 정전기 교육 자료 2001 년도 자료로 연식이 좀 되었는데, 이쪽 기술이 고만고만해요.. 왜 발전이 느린지 회로내의 과전압,과전류(Surge)로 인한 IC 파괴 대부분의 IC불량 유형임 기타 기사들 그리고, 검색된 좋은 기사도 여기에 저장. [SMT와 ESD 제어 기술 4] EOS/ESD 불량 분석, 이렇게 해결하라 [SMT와 ESD 제어 기술 4] EOS/ESD 불량 분석, 이렇게 해결하라 [SMT와 ESD 제어 기술 4] EOS/ESD 불량 분석, 이렇게 해결하라 www.hellot.net

IT/ASIC | FPGA 2019. 4. 25.

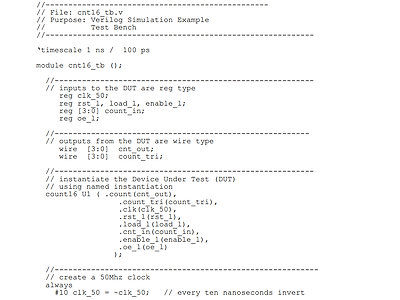

[HDL] Test Bench 작성가이드 in Verilog

이것저것, 책도 인터넷도 뒤져봐도 기본이 중요 첨부된 자료정도면 기본 이해 뿐 아니라 왠만한 건 그냥 해결 가능 카운터 테스트를 예제로 해서 자세히 설명되어 있음. 반드시 숙지한 후 작업에 적용하기 원본 소스 : http://people.ece.cornell.edu/land/courses/ece5760/Verilog/LatticeTestbenchPrimer.pdf 꼴랑 10페이지니깐, 다 외울 수도 있겠다. 모듈 인스턴스 정의하고, 맵핑하고, 클럭 정의해서 기본으로 주는 부분. 추가로 디버깅을 위해 출력하는 예제 부분만 살짝 캡처 초초 기본이니깐 너무 큰 기대는 말고, 다들 짜요~~

IT/ASIC | FPGA 2019. 4. 25.

반도체, 칩이 만들어 지는 과정

인텔에서 제공하는 자료네요. 걍 pdf로 첨부합니다. 이런것도 저작권법에 걸리려나.. 자료에 보면, 아래와 같이 모래에서 반도체로 가는 과정을 간략하게 도식화 해둠. 좀 예전 자료라 다시 찾아보면 더 좋은 자료가 많을 것 같지만, 일단 업데이트 현재 인텔 사이트에서 동영상으로 제공하고 있다 https://newsroom.intel.com/press-kits/from-sand-to-silicon-the-making-of-a-chip/#from-sand-to-silicon-the-making-of-a-chip 인텔 제공 반도체 제조 과정 제가 찾은건 아니고, 트랙백 겁니다. (Dr.Donny 님의 블로그에서 보고 올립니다. 감사^^)

IT/ASIC | FPGA 2018. 11. 28.

(2018)[IDEC 연구원 교육] Cell-Based 설계 Flow 교육

(2018)[IDEC 연구원 교육] Cell-Based 설계 Flow 교육 그리고, IDEC 의 강의 리스트에도 이 자료의 소개가 있다. (2018)[IDEC 연구원교육] Cell-based flow 교육 - http://www.idec.or.kr/vod/apply/view/?&no=144 [강좌 개요] - 디지털 칩 설계 전체 과정 중, 본 과정은 Front – End 과정을 다루는데 초심자의 눈높이에 맞추어 이론과 실습을 진행함. 기존의 Front-End 강좌에 Verdi Verification과정을 추가하여 새롭게 업데이트 했습니다 - IC Compiler 를 이용한 Layout 방법을 소개하고 Back-end 과정 진행 시 주의 사항에 대해서 학습할 수 있도록 합니다. [사전지식] 디지털 논리회로..