IT/ASIC | FPGA 2017. 5. 31.

[전자 기초] MOSFET의 원리

[전자 기초] MOSFET의 원리 트랜지스터 원리, 알고보면 간단해요^^ 트랜지스터 원리, 알고보면 간단해요^^ | 삼성디스플레이 뉴스룸 우리가 사용하고 있는 스마트폰, 태블릿PC, 데스크탑PC 등 셀수 없이 많은 전자 기기에 반도체가 들어가죠? news.samsungdisplay.com 중요한 것만 캡쳐. 원본글로 들어가서 보세요 자세한 것은 만화로 쉽게 이해하는 모스펫(MOSFET)의 스위칭 동작 원리 만화로 쉽게 이해하는 모스펫(MOSFET)의 스위칭 동작 원리 중학교 과학시간에 배운 전자회로에서 전압이 조금 걸리면 전류도 조금 흐르고, 전압이 많이 걸리면 전류도 많이 걸린다는 점을 기억하시나요? 즉, 전압이 걸린 이상 전류를 흐르지 않게 할 수는 없다는 말인데요.. blog.skhynix.com ..

IT/ASIC | FPGA 2017. 5. 26.

인터뷰 예상 질문 - 반도체 설계 인력

이런 대단한 블로거가 있나? 반도체 설계자들이 인터뷰 준비를 위한 예상 질문리스트 (답변은 일부 있음) 정리해 놓은 글 발견세세히 다 알지는 못하지만 자기 분야에 맞는 글을 읽어보고 정리해 보면 쵝오~~Backend (Physical Design) Interview Questions and AnswersMar 12, 2008 ... Backend (Physical Design) Interview Questions and Answers. Below are the sequence of questions asked for a physical design engineer.asic-soc.blogspot.com/2008/.../backend-physical-design-interview.htmlCompanywis..

IT/ASIC | FPGA 2017. 5. 26.

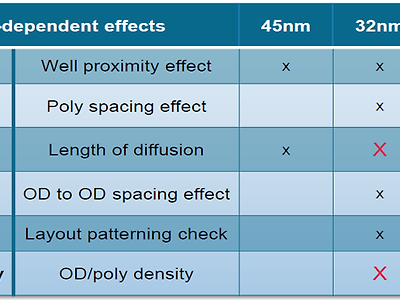

Temperature inversion

Temperature inversion – concept and phenomenon(http://vlsiuniverse.blogspot.kr/2015/04/temperature-inversion-deep-dive-into.html)머 공정이 낮아질수록 변수가 복잡해짐.단순히 온도가 낮고 높은 온도이면 best case 인데. 잘은 모르지만 공정이 낮아지면 원칙에서 벗어나 온도가 높아도 가끔 best case의 범위를 넘는 것들이 나오는 경우도 있음. 당연히 그 반대의 경우도 생각해야 하고...단어만으로 이해하면 이런 뜻이것 같은데. 머 틀려도 어쩔수 없지.시원한 바다가 생각나는 여름이~~출처: https://pixabay.com/en/santorini-oia-greece-water-1571484/

IT/ASIC | FPGA 2017. 5. 26.

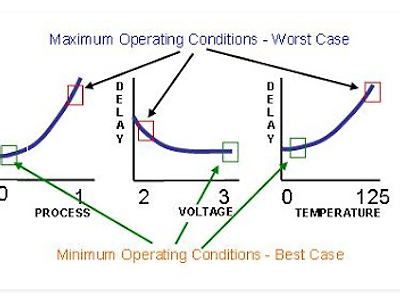

Process-Voltage-Temperature (PVT) Variations and Static Timing Analysis

참고글 소개, 너무 기술적인 내용이라 읽기는 싫지만 가끔은 찾아봐야 함(http://asic-soc.blogspot.kr/2008/03/process-variations-and-static-timing.html)Sources of variation can be:Process variation (P)Supply voltage (V)Operating Temperature (T)The best and worst design corners are defined as follows:Best case: fast process, highest voltage and lowest temperature 빠른 공정, 높은 전압, 낮은 온도Worst case: slow process, lowest voltage and hig..

IT/ASIC | FPGA 2017. 5. 25.

[전자] EOS / ESD - 기초 지식

관련글 링크 2016/02/26 - [IT/ASIC | FPGA] - [반도체] ESD Test - HBM,MM,CDM 자료 모음 2017/07/18 - [IT/ASIC | FPGA] - ASIC, SoC, 반도체, 설계 관련 글 모음 EOS 와 ESD 에 대한 기초지식 네이버 블로그 검색으로 해결~ http://blog.naver.com/bkpark777/80164645562 ESD에 대해서 서지 (surge)와 ESD의 차이점이 뭔가요? ESD는 Electrostatic Discharge 의 약자로서 정전기를 방... blog.naver.com EOS(electriocal overstress : 전기적 과부하)의 일반 용어로 볼 수 있고, EOS는 번개(lightning), 전기자기파(EMP), 정전..

IT/ASIC | FPGA 2017. 5. 25.

[Tool] ANSYS PathFinder

ESD / EOS 관련 이야기가 막 나오니깐..패쓰파인더라는 툴이야기가 나오네. ESD는 기존의 관련 글 참고 : ESD Test - HBM,MM,CDM (http://ts.devbj.com/425)ANSYS (자회사 Apache) 에서 나오는 Pathfinder . 정보는 일단 간단한 코멘트와 저장을 해 두어야 나중에 가치가.https://www.apache-da.com/products/pathfinderANSYS PathFinder is an electrostatic discharge (ESD) planning, verification and sign-off solution for full-chip SoC and IP designs. It is applied in layout and circuit-l..

IT/ASIC | FPGA 2017. 3. 31.

[기초] What is Tape out?

What is Tape-out ? 반도체 설계를 하다보면, Tape out 이라는 용어를 접하게 된다. 머 쉽게. 최종 결과물을 공장으로 내보내는 것을 말한다고 보면 된다. 이후에는 마스크를 실제 제작하게 되므로, 수정이 필요한 경우에 많은 비용을 감수해야 한다. 고로, Tape-out 이전에 꼭 잘 검증해야 한다는 것.. 어디선가는 PG 라고도 하는데 이는 Pattern Generation 의 약자로 같은 의미로 보면 된다. 근데 왜 tape out 인가? from : http://egloos.zum.com/analogwise/v/951048 이제, 설계한 제품을 마치고 공장으로 보내는 과정이 tape out이다. 일전에는 정말도 tape를 들고 뛰었다. 학교에서 공부할 때의 초창기에는 reel tap..

IT/ASIC | FPGA 2017. 3. 21.

Shmoo Plot, Shmoo Hole 에 대한 간단한 설명

Shmoo Plot, Shmoo Hole 에 대한 간단한 설명 반도체 칩 테스트 관련해서 이런 용어들이 많이 등장한다. 보통은 구글링을 하면 한글을 보기 힘든데 친절하게 정리해 두신 분이 그냥 링크를 거는 것이 나을 듯 하다. Shmoo Plot에 대한 간단한 설명 shmoo plot을 그리는 방법에 대해서 먼저 설명을 해 보겠습니다. shmoo plot은 생산된 반도체 칩이 여러가지 조건의 조합(보통은 전압과 동작속도일 경우가 많습니다.)에서 정상동작을 하는지 여부를 측정한 결과를 모아서 2차원의 그래프로 보여주는 것입니다. 윗 그림에서 가로축이 동작속도, 세로축이 전압이라고 가정하면 얻어진 shmoo plot은 각 칸의 위치에 해당하는 전압과 동작속도 조합에서 특정한 test vector의실행 결과를..

IT/ASIC | FPGA 2016. 11. 17.

Flipchip vs wire bond

Flipchip vs wire bond 무조건 모든 칩들을 하나의 실리콘 다이로 올릴 수는 없다. Fab 특성, 공정에 따라 어쩔 수 없이 Die 가 나누어 질 수 밖에 없는 경우가 있다.이 경우, SiP를 해야 하는데 일단 대표적으로 2개의 방법을 알고 싶어 조사.머 어렵게 말고 그림 하나로 해결.. 그림출처 : http://images.slideplayer.com/18/5765728/slides/slide_35.jpg 이상 자세한 내용은 시간 있을 때 따로 정리..

IT/ASIC | FPGA 2016. 9. 26.

반도체 공정 쉽게 알기 - 삼성반도체이야기 링크

반도체 공정을 아주 쉽게 잘 설명해 둔 링크 반도체 공정 이해하기 from 삼성반도체이야기 블로그반도체 8대 공정 1탄. 반도체 집적회로의 핵심재료, 웨이퍼란 무엇일까요? 반도체 8대 공정 2탄. 웨이퍼 표면을 보호하는 산화공정(Oxidation) 반도체 8대 공정 3탄. 전자산업의 혁명, 집적회로(IC, Integrated Circuit) 반도체 8대 공정 4탄. 웨이퍼에 한 폭의 세밀화를 그려 넣는 포토공정(Photo) 반도체 8대 공정 5탄. 특정 회로패턴을 구현하는 식각공정(Etching) 반도체 8대 공정 6탄. 반도체가 원하는 전기적 특성을 갖게 하려면? 반도체 8대 공정 7탄. 전기를 통하게 하는 마지막 작업, 금속 배선 공정 반도체 8대 공정 8탄. 합격으로 가는 첫 번째 관문 EDS(El..

IT/ASIC | FPGA 2016. 9. 22.

edge detect pulse - 트리거된 이벤트를 알아내 한 클럭 pulse 만들기

머 제목부터 어렵다.정하기가..국어가... 왜 - 시나리오어떤 신호가 '1' 인 상태로 여러 클럭에 걸쳐져 있다.그런데 나는 '0' 에서 '1'로 올라간 이벤트를 알려주는 것처럼 한 번의 사건에 한 클럭만큼의 이벤트 펄스를 만들기를 원한다.해결은 그림으로이렇게 하면 된다. 즉 그림의 OUT 신호를 보고 사용하면 해결~~그림은 남이 그린 것이므로 원본글의 위치를 알려드립니다.보시고 HDL 코드도 필요하다고 생각하시면 해당글에 가셔서 꼭 읽어보세요. http://www.boldport.com/blog/2015/4/3/edge-detect-ad-nauseam 즐~~