Xilinx Vivado로 만들어지 bit 파일을 이제 실제 FPGA 에 올려서 보드 테스트를 해보자.

이과정도 툴 마다 달라서 일단 정리해 둔다.

먼저 여러 단계를 각각 누르지 말고, "Generate Bitstream" 을 그냥 확 누른다.

즉, 합성, P&R, 구현 다 한꺼번에 수행한다.

코드가 변경되어서 합성부터 구현까지 다시 하겠다는 창이다. 그냥 "Yes" 누르면 진행된다.

얼마나 빨리 하려고 이런걸 묻나 그냥 기본값을 4를 두고 오케이

본격적으로 합성을 수행하고 있음을 알수 있다. "Project Summary" 창에서 보면 현재 진행되는 과정을 볼 수 있다.

에러가 없다는 아래 메시지 창이 등장한다. 이제 다했으니 머할까요? 이런 창이다.

FPGA에 bit를 올리기 위해 "Open Hardware Manager"를 클릭한다.

보드가 연결되어 있다면 "Open Target"을 수행하여 FPGA Jtag 을 연결해야 한다. 아래 화살표가 가리키는 2개 중에 아무거나 클릭해도 된다.

세상은 "Auto" 가 좋다.

자동 연결을 수행하면, 아래 그림처럼 Xilinx FPGA가 정상으로 연결되었음을 볼 수 있다.

이제 만들어진 Bit 를 구우면 (올리면 된다)

자동을 잡힌 보드 Digilent 아래에 보면 FPGA 칩셋 모델명이 나온다.

선택하고 오른쪽 버튼 누르고, "Program Device" 선택한다.

만들어진 Bit 를 선택하고 (Path를 다시 확인해 보는 것도 좋다)

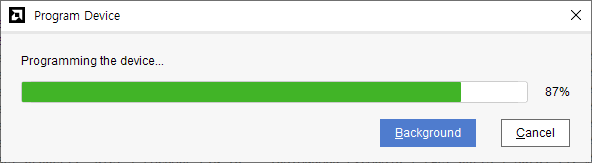

그럼 Program 이 되면서 자기가 만든 코드가 바로 FPGA에서 동작하기 시작한다.

물론 로직이 잘 만들어 졌다면 말이다.

지금까지 Xilinx Vivado 툴을 이용하여 FPGA에 bit 를 올려서 실행하는 방법을 알아봤다. 이건 툴 사용법이지 로직 설계는 아니니 일단은 로직을 잘 만듭시다. 도움이 되는 글이길 :)

PS) FPGA에 Bit를 올렸다고 사실 끝은 아니다. 왜냐하면 이건 그냥 RAM에 올렸다고 생각하면 된다. 파워 전원을 끄면 다시 깡통이 되는 것을 꼭 인지하기 바란다. 전원이 다시 켜져도 같은 로직이 동작하기를 원하는 사람은 Flash, EEPROM 용 bit를 생성해서 해당 메모리에 구워둬야 한다. :) 기본이니깐 다 알듯

'IT > ASIC | FPGA' 카테고리의 다른 글

| Xilinx Vivado - 다운로드 및 설치 (1) | 2024.02.13 |

|---|---|

| Verilog - flatten array - 2차원 배열 1차원으로 변환 (1) | 2024.02.05 |

| Xilinx Vivado - 핀 할당 하기 Constraints 추가 (0) | 2024.02.02 |

| Xilinx Vivado - FIFO Generator 로 사용자 FIFO 만들기 (0) | 2024.02.02 |

| Xilinx JTAG – HS2, HS3, Platform Cable USB II (0) | 2024.01.25 |