IT/ASIC | FPGA 2024. 2. 20.

Verilog - Parameter, deparam 사용법

모듈내에 데이터 비트등을 선언할때 정의를 하도록 하려면 Parameter 방법을 이용해야 한다. Hard-fix 코드로 박아두면 항상 문제가 생기곤 했다. 귀찮아도 꼭 미리 해두자 Parameter 선언 인스턴스 생성시에 데이터 비트를 지정하게 하는 방법은 모듈을 만들때 아래처럼 파라메터 값을 받아 처리하도록 하는 것이다. C/C++ 코드의 생성자 함수내의 파라메터를 같은 개념이지 module #() ; 아래 예제는 여기서 가져왔다. https://docs.xilinx.com/r/en-US/ug901-vivado-synthesis/Parameters-Example-Verilog module myreg (clk, clken, d, q); parameter SIZE = 1; input clk, clken; ..

IT/ASIC | FPGA 2024. 2. 20.

Xilinx Vivado - SPRAM, DPRAM, block RAM 활용

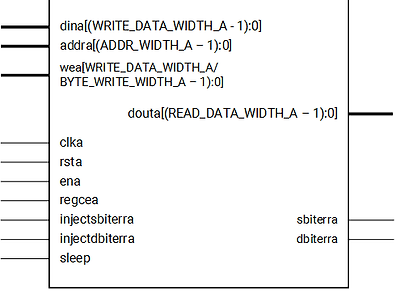

FPGA 는 내부의 램을 필요한 만큼 만들어 쓸수 있는 장점이 있다. 기본적인 1 포트 램을 만들어서 써보자. 일단 데이터시트에서 동작도를 확인할 필요가 있다. Xilinx Parameterized Macros 페이지에 가면 기본적인 RAM에 대한 정보가 있다. https://docs.xilinx.com/r/en-US/ug953-vivado-7series-libraries/XPM_MEMORY_SPRAM XPM_MEMORY_SPRAM - 2023.2 English Specify the reset value of the port A final output register stage in response to rsta input port is assertion. Since this parameter is a ..

IT/ASIC | FPGA 2024. 2. 16.

Verilog - Metastable, CDC (clock domain crossing) 정리

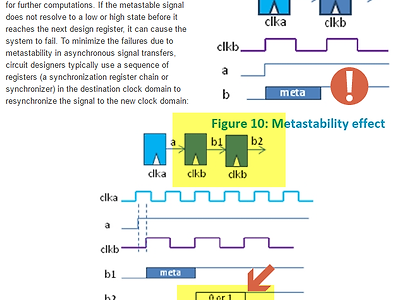

ASIC, FPGA 설계시에 CDC clock domain crossing 내용을 알고 있는지 물어보는 사람이 많은 것 같네요. 제가 알고 있는 방법이 너무 간단해서 이게 꼭 공고에 나올만한 내용인지 모르겠지만 (내가 모르는 무엇인가가 엄청 있는건가요? ^^;;;;) 결론적으로, 클럭이 다른 도메인 사이의 시그널 교환에서는 반드시 무조건 필수적으로 metastable 상태가 전달 되지 않도록 Multi-stage synchronizer 를 사용하면 해결된다는 것!! 참고한 글은 유명한 블로그 님들의 글입니다. https://secondspot.tistory.com/18

IT/ASIC | FPGA 2017. 7. 18.

ASIC, SoC, 반도체, 설계 관련 글 모음

ASIC, SoC, 반도체, 설계 관련 글 모음 여러군데, 혹은 여기에 단편적으로 적어두다 보니 목차같은 페이지가 없다. 좀 정리가 안되더라도 한 페이지에 모아서 저장해 두면 좋겠다 생각하던 차에 Github pages 를 이용하여 jekyll 블로그를 하나 만들어서 해당 페이지를 만들어 두었다. 업데이트 열심히 해야지 ASIC, SoC, 반도체, 설계 관련 글 모음 (http://devbj.com/asic/) ASIC ASIC Design Tutorials - 위키사이트, 전체흐름을 살펴보자. 설계, FPGA, 검증. HDL 설계에 사용되는 hdl 언어(VHDL, Verilog, SystemVerilog, …) 관련 자료를 모아두자. Verilog http://www.testbench.in/ - 테스트..

IT/ASIC | FPGA 2017. 6. 30.

PV - Physical verification / DRC, LVS, ERC, DFM

PV - Physical verification / DRC, LVS, ERC, DFM개발 보단 검증의 시대.검증이라는 것은 끝이 없는 터.. 어느 정도 기준을 세워서 그만 할 수 있어야 하는 용기가 필요..참고: https://www.synopsys.com/news/pubs/compiler/artlead_design-sep05.html?cmp=NLC-compiler&Link=Sep05_Issue_Art1무튼..용어들을 살펴보자.DRC - Design Rule Check기본적으로 파운드리가 제공하는 룰이 있다. 그 룰에 위배 되는지 아닌지 판단하면 된다.Consists of dimensional rules (width/spacing/coverage landing) for metals, diffusion, ..

IT/ASIC | FPGA 2016. 9. 22.

edge detect pulse - 트리거된 이벤트를 알아내 한 클럭 pulse 만들기

머 제목부터 어렵다.정하기가..국어가... 왜 - 시나리오어떤 신호가 '1' 인 상태로 여러 클럭에 걸쳐져 있다.그런데 나는 '0' 에서 '1'로 올라간 이벤트를 알려주는 것처럼 한 번의 사건에 한 클럭만큼의 이벤트 펄스를 만들기를 원한다.해결은 그림으로이렇게 하면 된다. 즉 그림의 OUT 신호를 보고 사용하면 해결~~그림은 남이 그린 것이므로 원본글의 위치를 알려드립니다.보시고 HDL 코드도 필요하다고 생각하시면 해당글에 가셔서 꼭 읽어보세요. http://www.boldport.com/blog/2015/4/3/edge-detect-ad-nauseam 즐~~

IT/ASIC | FPGA 2016. 9. 22.

CDC(Clock Domain Crossing) 설계시 반드시 들어가는 synchronizer

이전글에 이어 하나더, ASIC 설계시에 가장 중요한,실제 합성 후의 이상한 현상이 발생하는 경우 가장 많이 의심하는 이부분 CDC 설계에서 기본적인 것이라 볼 수 있다.그림으로 설명이 가능하다.물론 원본글은 아래 글에 방문하여 전체를 읽어 보는 것이 좋다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 무작정 다른 클럭의 시그널을 보고 사용하는 경우 Meta 상태의 값을 레퍼런스 할 수 있으므로이후 동작을 보장할 수 없다. 경우에 따라 다른 상황이 발생할 수도 있고, 잘 동작할 수도 있다. 운좋게.. 무튼, 그래서 무조건 F/F 2개 정도를 clock domain 사이에 넣어주는 것이 일반적인 기법..