IT/ASIC | FPGA 2024. 2. 15.

Verilog - 파이썬으로 테스트 벤치 작성하기 cocotb - 킵

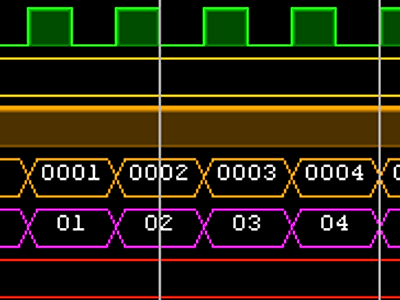

파이썬으로 테스트벤치를 작성하도록 도와주는 파이썬 프로젝트가 있어 일단 킵 이름은 cocotb 라고 하네 공식 사이트는 여기 https://docs.cocotb.org/en/stable/index.html cocotb cocotb is a COroutine based COsimulation TestBench environment for verifying VHDL and SystemVerilog RTL using Python. 일단 지원되는 시뮬레이터 종류는 다음과 같다. cocotb 기본 골격 A typical cocotb testbench requires no additional HDL code. The DUT is instantiated as the toplevel in the simulator wi..

IT/ASIC | FPGA 2024. 2. 15.

Verilog - RGMII 샘플 코드 - 북마크

Verilog 로 구현된 RGMII 코드가 있어서 일단 공유한다. RGMII 는 이데넷 PHY칩과 MAC 사이의 통신 방법이라고 보면 된다. 일단 아래 블로그글을 참고하자. https://www.circuitden.com/blog/23 CircuitDen | Artin Isagholian This article is for hardcore digital design wizards who don’t want to use any intermediate processors (kiss your software team goodbye) or proprietary IPs to communicate with their FPGAs via an ethernet connection. All you need is a PC,..

IT/ASIC | FPGA 2024. 2. 15.

Verilog 기초 - case 문

Verilog 기초 문법과 관련된 것도 하나씩 정리해 보자. 오늘은 case 문이다. if 문과는 다르게 병력적으로 우선순위 없이 생긴다는 장점이 있다. 반드시 우선순위가 필요하다면 if else 문을 사용해야 하며, 같은 조건에서 mux 하는 로직 같은 경우에는 case 문을 활용하면 된다. 아래 문법과 예제는 다음 사이트에서 참고하였다. https://vlsiverify.com/verilog/case-statement/ Case 문법 기본 문법은 다음과 같다. case() : : : : begin ... ... end default: endcase 사실 예제로 보는 게 가장 낫다. Case 예제 module case_example; reg [2:0] data; always @(data) begin c..

IT/ASIC | FPGA 2024. 2. 13.

Xilinx Vivado - 다운로드 및 설치

FPGA 에 프로그래밍 할 수 있는 툴인 Vivado를 다운로드 하고 설치해 보자. 사용자 계정 생성 우선 툴 제공 업체인 AMD 사이트에서 계정을 먼자 만들고 로그인 해야 한다. 계정 생성하는 방법은 AMD 사이트에서 로그인 버튼은 누르면, 아래와 같이 생성할 수 있는 "계정 만들기" 버튼을 볼 수 있다. 클릭해서 생성작업을 해보자. 정보를 입력하고 생성이 완료되면, 꼭 로그인을 하도록 한다. Vivado Download 이제 Vivado 툴을 다운로드 하면 된다. 해당 툴을 다운로드 하는 경로는 아래와 같다. 다운로드 주소https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tool..

IT/ASIC | FPGA 2024. 2. 5.

Verilog - flatten array - 2차원 배열 1차원으로 변환

Verilog 에서 포트로 넘길때 2차원 배열이 되지 않는다는 슬픈 진실이 있네 ㅜㅜ 일단 보통 합성할 때 합성툴에서 다 자동으로 해줄 듯 한데 이를 손으로 해야 한다니 일단 방법은 알아두자고 https://stackoverflow.com/questions/28623819/how-to-flatten-array-in-verilog How to flatten array in Verilog As Verilog does not allow to pass the array as input to module, so how can we flatten any array in Verilog. Suppose I have this array: parameter [31:0] A [0:31]; wire [31:0] B I wan..

IT/ASIC | FPGA 2024. 2. 2.

Xilinx Vivado - FPGA 에 bit 생성해서 올리기 - 보드 테스트

Xilinx Vivado로 만들어지 bit 파일을 이제 실제 FPGA 에 올려서 보드 테스트를 해보자. 이과정도 툴 마다 달라서 일단 정리해 둔다. 먼저 여러 단계를 각각 누르지 말고, "Generate Bitstream" 을 그냥 확 누른다. 즉, 합성, P&R, 구현 다 한꺼번에 수행한다. 코드가 변경되어서 합성부터 구현까지 다시 하겠다는 창이다. 그냥 "Yes" 누르면 진행된다. 얼마나 빨리 하려고 이런걸 묻나 그냥 기본값을 4를 두고 오케이 본격적으로 합성을 수행하고 있음을 알수 있다. "Project Summary" 창에서 보면 현재 진행되는 과정을 볼 수 있다. 에러가 없다는 아래 메시지 창이 등장한다. 이제 다했으니 머할까요? 이런 창이다. FPGA에 bit를 올리기 위해 "Open Hard..

IT/ASIC | FPGA 2024. 2. 2.

Xilinx Vivado - 핀 할당 하기 Constraints 추가

Xilinx Vivado에서 원하는 핀을 할당 하려면 Constraints 파일을 추가해야 한다. 아니면 랜덤으로 막 핀을 Assign 하므로 하드웨어설계도와 맞출 필요가 있다. 참고로, FPGA하드웨어 핀을 선택하기 위해서는 기본적으로 어떤 핀을 뽑아야 할지 처음에는 랜덤으로 돌린 후에 하드웨어 설계를 진행하는 경우가 일반적이다. 아무튼 핀 할당을 해보자. 위의 그림처럼 수정하기를 눌러본다. 새로 만드는 것이므로 과감하게 "Create File"을 누른다. 나타나는 창에 원하는 이름만 딱 쓰고, OK 하면 그럼 다음과 같이 파일이 하나 생성됨을 볼 수 있다. 그럼 왼쪽 트리창에 하나 추가되어 있는데, 아시다시피 빈파일이다. 전구 모양 버튼 "Language Template" 을 누르면 기본 문법 구문을..

IT/ASIC | FPGA 2024. 2. 2.

Xilinx Vivado - FIFO Generator 로 사용자 FIFO 만들기

Xilinx Vivado 툴에서 제공되는 FIFO Generator 로 사용자 FIFO 만들기를 그냥 한번 해보고, 그림을 남겨둔다. FPGA는 참 어찌보면 쉽다. 이렇게 마법사로 FIFO를 원하는 대로 만들어 낼 수 있다니 8비트 UART 송수신용 FIFO가 필요해서 일단 IP 검색에서 FIFO Generator 를 선택하면 더블 클릭하거나 엔터를 치면 아래와 같은 창이 나타난다. 일단, 아무것도 하지 말고 자기가 원하는 이름만 변경하자. 이제 원하는 데이터 비트를 8비트로 변경해 보자. 위의 그림에서 "Native Ports" 라는 부분을 클릭하면, 아래 창이 나타난다. 아무것도 건드리지 말고 Data Port 만 수정하자. Width 를 8 로 변경하고 Tab을 누르면 아래 Read Width도 자..

IT/파이썬 2024. 2. 2.

Pydantic none 오류 처리 방법 - Optional 사용

Django ninja 로 API Schema를 만드는데 None type으로 정희한 부분에서 에러가 발생했다. Null이 들은 필드의 값을 받아오는 Schema에서 기본값으로 None을 주면 Exception이 발생하지 않은 것 같은데 갑자기 발생하네 response.items.1.manager2_position Input should be a valid string [type=string_type, input_value=None, input_type=NoneType] For further information visit https://errors.pydantic.dev/2.6/v/string_type 에러 내용은 대충 이러했다. class ProductInSchema(ModelSchema): note..

IT/Software 2024. 1. 26.

SNMP - 용어 이해와 Arduino C 프로젝트들

SNMP(Simple Network Management Protocol) 는 UDP 기반 프로토콜인데, TCP 처럼 서버 클라이언트 구조를 가지는 형태다. 그냥 서버 클라이언트라는 용어를 쓰면 좋겠는데, 매니저 에이전트 이런 용어를 사용한다. 개괄적인 내용은 아래글에 정리가 잘 되어 있으니 확인해 보고, https://aws-hyoh.tistory.com/179 SNMP 쉽게 이해하기 #1 제 친구 중에 초등학교 교사가 있습니다. 하는 말을 들어보니 예전보다야 학생 수는 줄었지만 돌보고 가르치는 것은 더더욱 어렵다고 합니다. 요즘 같이 교권이 바닥에 추락한 현실에 한창 뛰어 aws-hyoh.tistory.com https://itragdoll.tistory.com/43 [Network] 네트워크용어 - ..

IT/ASIC | FPGA 2024. 1. 25.

Xilinx JTAG – HS2, HS3, Platform Cable USB II

Xilinx JTAG 케이블 종류가 많은데 숫자가 보통 높은걸로 선택하는데 이것은 JTAG HS2 가 호환성이 더 좋은듯 Digilent FPGA 보드를 많이 쓰니, 해당 회사에서 만든 제품으로 알아보자!! https://digilent.com/reference/programmers/jtag-hs2/reference-manual?_ga=2.209894997.1913691520.1700123539-2102363698.1698815413#supported_target_devices Is JTAG-HS2 is compatible with Artix 7 series FPGA? @vertika.s, Yes, it is compatible. You can view the full supported Artix 7 시..

IT/IoT | Hardware 2024. 1. 19.

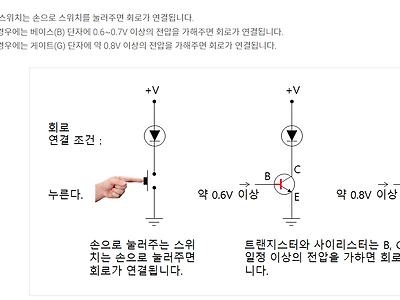

전자전기 - SCR 제어

전자 전기 SCR 제어 방법에 대해서 알아보다가, SCR이 머야? https://javalab.org/breadboard_thyristor_switch/ 6-4 사이리스터(SCR)를 활용한 스위치 - 자바실험실 택트 스위치를 한번 눌렀다 떼면 LED에 불이 들어옵니다. 스위치에서 손을 떼고 있어도 불은 계속 켜져 있습니다. 스위치를 계속 누르고 있지 않아도 됩니다. 클릭하여 3D 모델링 화면을 회전시켜 javalab.org 사이리스터(Thyristor)는 트랜지스터와 비슷한 기능을 하는 스위칭 소자입니다. ‘사이리스터’를 ‘실리콘 제어 정류기(Silicon-controlled rectifier, 줄여서 SCR)’라고 부르기도 합니다. 정식명칭은 ‘사이리스터’입니다. 완벽한 그림 설명이다. 감탄!! SCR..