IT/IoT | Hardware 2024. 4. 3.

DDR 인터리빙?

DDR 인터리빙(DDR Interleaving)은 메모리 접근 방식을 최적화하여 전체 시스템의 성능을 향상시키는 기술입니다. 이 기술은 DDR(Double Data Rate) SDRAM 메모리 모듈 사이에서 데이터를 분산시켜 저장하고, 이를 통해 메모리 대역폭을 효율적으로 활용하게 합니다. 인터리빙은 메모리 채널을 통해 데이터를 교대로 읽고 쓰는 방식으로, 메모리 접근 시간을 단축하고 처리량을 증가시킵니다. 인터리빙의 종류 채널 인터리빙(Channel Interleaving): 여러 메모리 채널을 사용하여 데이터를 분산시키는 방식입니다. 이를 통해 다수의 메모리 모듈이 동시에 작업을 처리할 수 있게 되어, 전체적인 메모리 접근 속도와 시스템 성능이 향상됩니다. 뱅크 인터리빙(Bank Interleavin..

IT/리눅스 2024. 4. 3.

리눅스 - sed를 이용해서 한꺼번에 특정 문자열을 바꾸는 명령

리눅스 환경에서는 sed (Stream Editor) 명령어를 사용하여 파일 내의 특정 문자열을 찾아 바꾸는 작업을 할 수 있습니다. 여러분이 원하는 -timescale=1ns/1ps 문자열을 timescale=1ns/1ns로 바꾸고자 할 때, 특정 확장자(.csh)를 가진 파일들에 대하여 이 작업을 적용하려면, find 명령어와 sed를 결합하여 사용할 수 있습니다. 다음은 이를 위한 한 가지 방법을 제시하는 명령어 스크립트 예시입니다: find . -type f -name "*.csh" -exec sed -i 's/-timescale=1ns\/1ps/timescale=1ns\/1ns/g' {} + 이 명령어는 다음과 같이 작동합니다: find . -type f -name "*.csh":..

IT/Software 2024. 4. 2.

VI 팁 - 특정 문자열 포함 라인 전체 없애기

vi나 vim 내부에서 문자열을 찾아 삭제하는 명령어들을 사용할 수 있는데, 이는 sed 명령어를 사용하는 것과는 조금 다른 방식입니다. vi나 vim에서는 파일을 직접 수정하면서 볼 수 있는 장점이 있습니다. 단일 줄에서 문자열 삭제하기 vi나 vim에서 특정 문자열을 포함하는 모든 줄을 삭제하려면, 다음과 같은 명령을 사용할 수 있습니다: :g/특정문자열/d이 명령은 "특정문자열"을 포함하는 모든 줄을 찾아서 삭제합니다. g는 전역(global) 검색을 의미하며, /d는 삭제(delete)를 의미합니다. 줄바꿈을 포함하는 문자열 삭제하기 vi나 vim에서 줄바꿈을 포함하는 문자열을 삭제하는 것은 직접적으로는 지원되지 않습니다. 하지만 줄바꿈 문자를 직접 찾아서 다루는 대신, 연속된 줄들을 하나의 줄로..

IT/Software 2024. 3. 29.

VI 기능 - 문자열에서 바로 파일 열기 - gf

Vi나 Vim에서 특정 문자열 위치에 가서 그 문자열과 같은 이름을 가진 파일을 바로 여는 기능은 몇 가지 단계를 거쳐서 사용할 수 있습니다. 다음은 기본적인 방법입니다: 문자열 검색: 먼저, 파일 내에서 찾고 싶은 특정 문자열을 검색해야 합니다. /문자열 명령어를 사용해서 검색할 수 있습니다. 여기서 문자열은 찾고자 하는 문자열입니다. 커서 이동: 검색된 문자열 위치로 커서가 이동하면, 그 문자열이 포함된 라인에 커서가 위치하게 됩니다. 문자열과 같은 이름의 파일 열기: 이제 그 문자열과 동일한 이름을 가진 파일을 열기 위해, gf (go to file) 명령을 사용할 수 있습니다. 이 명령은 현재 커서 위치의 단어나 문자열을 파일 이름으로 간주하고 그 파일을 엽니다. 단, 이 파일이 현재 작업 중인 ..

IT/ASIC | FPGA 2024. 2. 22.

FPGA - Nexys A7 보드 터미널 설정 on Windows

Digilent Board를 사용할 때 터미널 설정 법을 Xilinx 페이지에서 가져옴 원본 링크는 여기 => https://digilent.com/reference/programmable-logic/guides/serial-terminals/windows 먼저, 테라텀을 받아서 설치하고 난 뒤에 아래 내용대로 설정하면 된다. Open Tera Term's site (https://ttssh2.osdn.jp/index.html.en) in a new tab. Find the section of the page entitled “Download”. Select the “download page”. Then select the newest version exe installer. 1. New Connecti..

IT/ASIC | FPGA 2024. 2. 22.

Xilinx – PROM mcs 설정 – spi buswidth clock 조정

부팅 후 Done 시그널이 뜨는데 너무 늦게 뜬다. 그럼 bit 만들때 .xdc 파일에 설정을 해 줘야 한다는 것이 핵심 QSPI 를 쓸 수 있게끔, 매뉴얼로 세팅이 필요하다. spi x1 모드에 3MHz 클럭으로 잡혀 있어서 bit 크기에 따라 엄청 느릴수도 있다. Vivado 같은 툴에서 Implementation design 이 뜬 상태에서 Device configuration 이 활성화 되면 그쪽에서 수정할 수도 있고 아래 레퍼런스 처럼 그냥 .xdc 파일에 들어가서 수정을 직접 해줘도 된다. https://aifpga.tistory.com/entry/Vivado-mcs-%ED%8C%8C%EC%9D%BC-%EB%A7%8C%EB%93%A4%EA%B8%B0-Memory-Configuration-Fil..

IT/ASIC | FPGA 2024. 2. 20.

Verilog - Parameter, deparam 사용법

모듈내에 데이터 비트등을 선언할때 정의를 하도록 하려면 Parameter 방법을 이용해야 한다. Hard-fix 코드로 박아두면 항상 문제가 생기곤 했다. 귀찮아도 꼭 미리 해두자 Parameter 선언 인스턴스 생성시에 데이터 비트를 지정하게 하는 방법은 모듈을 만들때 아래처럼 파라메터 값을 받아 처리하도록 하는 것이다. C/C++ 코드의 생성자 함수내의 파라메터를 같은 개념이지 module #() ; 아래 예제는 여기서 가져왔다. https://docs.xilinx.com/r/en-US/ug901-vivado-synthesis/Parameters-Example-Verilog module myreg (clk, clken, d, q); parameter SIZE = 1; input clk, clken; ..

IT/ASIC | FPGA 2024. 2. 20.

Verilog - 숫자 표현 정리 - Signed vector 내용 중요

(작성중입니다) 숫자에 대한 verilog 표현에 대해서 알아본다. 원본 소스 글은 여기이다. 제 공부로 적당히 지워가며 정리된 것이니 꼭 원본 글로 방문해서 제대로 된 글을 읽어보시길 바랍니다. Numbers in Verilog Binary in Verilog By default, a Verilog reg or wire is 1 bit wide. This is a scalar: 기본으로 선언은 1 비트 길이를 표현한다. wire x; // 1 bit wire reg y; // also 1 bit logic z; // me too! A vector is declared like this: type [upper:lower] name; 벡터 값은 아래와 같이 표현된다. wire [5:0] a; // 6-bi..

IT/ASIC | FPGA 2024. 2. 20.

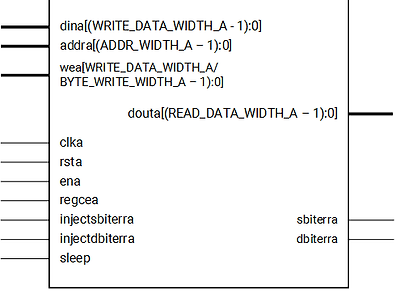

Xilinx Vivado - SPRAM, DPRAM, block RAM 활용

FPGA 는 내부의 램을 필요한 만큼 만들어 쓸수 있는 장점이 있다. 기본적인 1 포트 램을 만들어서 써보자. 일단 데이터시트에서 동작도를 확인할 필요가 있다. Xilinx Parameterized Macros 페이지에 가면 기본적인 RAM에 대한 정보가 있다. https://docs.xilinx.com/r/en-US/ug953-vivado-7series-libraries/XPM_MEMORY_SPRAM XPM_MEMORY_SPRAM - 2023.2 English Specify the reset value of the port A final output register stage in response to rsta input port is assertion. Since this parameter is a ..

IT/ASIC | FPGA 2024. 2. 16.

Verilog - Metastable, CDC (clock domain crossing) 정리

ASIC, FPGA 설계시에 CDC clock domain crossing 내용을 알고 있는지 물어보는 사람이 많은 것 같네요. 제가 알고 있는 방법이 너무 간단해서 이게 꼭 공고에 나올만한 내용인지 모르겠지만 (내가 모르는 무엇인가가 엄청 있는건가요? ^^;;;;) 결론적으로, 클럭이 다른 도메인 사이의 시그널 교환에서는 반드시 무조건 필수적으로 metastable 상태가 전달 되지 않도록 Multi-stage synchronizer 를 사용하면 해결된다는 것!! 참고한 글은 유명한 블로그 님들의 글입니다. https://secondspot.tistory.com/18

IT/ASIC | FPGA 2024. 2. 16.

Verilog - 합성에 유리한 coding 스타일

HDL(Verilog, VHDL, ...) 머든 실제 합성이 설계한 대로 되지 않으면 완전 무용지물이다. 코딩때 부터 신경써야 하는데, 많이 까먹었네. 따로 정리한 문서를 찾아보자. 일단 아래글을 찾아와서, 정리해보자. (지금 정리중...읽고 내 생각 넣고 머 이렇게) 예제나 설명에 대한 자세한 내용은 아래 해당 블로그 님의 글을 방문해서 보심이 맞는것 같습니다. https://trts1004.tistory.com/12108949 일단은 제 개인 공부용으로 복사해서 정리중.... 추가로 자료가 하나더 있다. 엄청 기본적인것인데 5분이면 읽어본다. 함 읽어보자. 1. 블록도를 그려라, 라벨을 붙이고, 시그널 적고, width 명기하자. 2. 타이밍도를 그려라 최대한 자세하게 3. 합성 가능한 코드 템플릿(..

IT/ASIC | FPGA 2024. 2. 16.

Verilog - 곱셈이 합성이 되나요?

verilog에서 * operator를 사용하면 곱셈 전용 조합회로가 합성되는건가요? 이런 질문을 구글링에서 본적이 있다. 아무 생각없이 사용하다가, 타이밍 오류가 없으면 그냥 넘어갔던 것인데, 합성툴이 기본적인것은 컴포넌트가 있는 것 같아, 별로 개의치 않고 설계 했고, 프로토콜 설계에 있어서는 대부분 곱하기 나누기는 사용하지 않았었다. 아무튼 답변도 있어서 일단 저장 https://www.inflearn.com/questions/1065809/14%EC%9E%A5-%EC%A7%88%EB%AC%B8 네, 현업에서도 Verilog 로 곱셈을 기술할때, * 을 사용합니다. Synthesis (합성) 과정을 통해서, targeting 하는 공정 lib 에 있는 * (곱셈 layout) 을 사용하기 때문이고요..

IT/ASIC | FPGA 2024. 2. 15.

Xilinx - Vivado RAM 초기화 값 입력 - coe 파일

Vivado 에서 RAM을 만들때 초기값을 넣어 줄 수 있다. 파일 포맷은 coe 파일인데 Vivado 에서 바로 에디팅 할 수 있다. COE 파일 생성 그냥 그림으로 남겨둔다. 아래처럼 쓰면 된다. radix = 16; pattern = 3 0 3 1 0 1 1 3 0 2 2 2 3 0 1 1 3 0 3; 다른 예제 파일도 아래 링크에서 찾아볼 수 있다. https://docs.xilinx.com/r/2021.2-English/ug896-vivado-ip/COE-File-Examples ****************************************************************** ************* Example of Virtex Bit Correlator.COE ****..