IT/ASIC | FPGA 2016. 9. 22.

CDC(Clock Domain Crossing) 설계시 반드시 들어가는 synchronizer

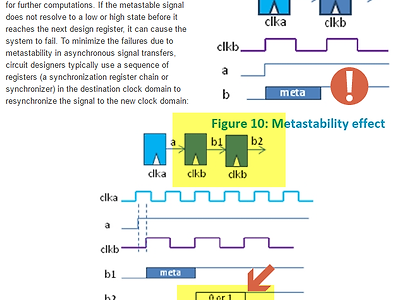

이전글에 이어 하나더, ASIC 설계시에 가장 중요한,실제 합성 후의 이상한 현상이 발생하는 경우 가장 많이 의심하는 이부분 CDC 설계에서 기본적인 것이라 볼 수 있다.그림으로 설명이 가능하다.물론 원본글은 아래 글에 방문하여 전체를 읽어 보는 것이 좋다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 무작정 다른 클럭의 시그널을 보고 사용하는 경우 Meta 상태의 값을 레퍼런스 할 수 있으므로이후 동작을 보장할 수 없다. 경우에 따라 다른 상황이 발생할 수도 있고, 잘 동작할 수도 있다. 운좋게.. 무튼, 그래서 무조건 F/F 2개 정도를 clock domain 사이에 넣어주는 것이 일반적인 기법..

IT/ASIC | FPGA 2016. 9. 22.

Recommended reset synchronization scheme

설계시 참고할 내용이 정말 많은 필수 페이지 일단 그중에서 필요한 내용은 바로 이것.원본글은 여기다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 이 그림이 뜻하는 바는 알고 가자. 리셋상태로 가는 것은 언제든지 async 한 조건으로 가고리셋에서 풀리는 경우에는 내부 시스템 클럭에 맞추어서 풀리도록 한다.여러 F/F 동작에 안정성을 부여할 수 있다. 즐

IT/ASIC | FPGA 2016. 7. 19.

Design compiler 관련 글 - Synopsys 합성 툴

Design compiler 관련 글 - Synopsys 합성 툴여기 저기 참 많이 있겠지만, 몇몇개 찾아서 본 자료들만 링크라도 모아 RTL 합성에 관련된 기본적인 내용이 잘 정리되어 있다. 아래 2개의 글만 숙지해도 문제가 없을 듯.Synthesis ABCs Part 1 - http://docslide.us/documents/syn-abc-part1.htmlSynthesis ABCs Part 2 - http://docslide.us/documents/syn-abc-part2.html그리고, 어렵게 찾아두는 한글 자료들. 열심히 하신 분들이 많이 계시네요. Design Compiler 정리 (http://blog.naver.com/PostList.nhn?blogId=beahey&from=postList..

IT/ASIC | FPGA 2016. 2. 26.

[반도체] ESD Test - HBM,MM,CDM 자료 모음

ESD Test - HBM,MM,CDM 관련 자료 모음 국내의 유명한 Faliunx 포럼의 글 중에.. (원본글 : ESD 정전기에 의한 반도체 불량) 하나-HBM (Human Body Model) 인체에 대전된 정전기 방전 수천 ~ 수만V 까지 대전된 작업자가 부품에 접촉하는 경우 정전기가 순간적으로 방전되어 수 KW의 전력이 흐르면서 부품을 파괴하게 됨 두울-CDM (Charged Device Model) 부품에 대전된 정전기 방전 부품의 운반, 보관, 취급 등의 과정에서 접촉성 대전이 이루어져 부품이 정전압을 유지하고 있다가 접지에 접촉되어 순간적으로 방전을 일으켜 파괴하게 됨. 세엣-FIM (Field Induced Model) 정전기장에 대전된 부품의 방전 전,자기장에 노출된 부품에서 IC 내부..

IT/ASIC | FPGA 2015. 12. 29.

Simulating verilog VHDL using Synopsys VCS - 칩 설계 검증 툴

Synopsys VCS 사용 - HDL compile & simulation, 칩 설계 검증 아래 2가지 원본 글을 가지고 아래와 같이 간단한 tutorial을 만들어 보았다. 한글이 곳곳에 보이도록 했다. 그래도 원본을 감상하시는 예의를 갖추도록.정리는 하고 있는 중인데, 자료는 쓸만해서 그냥 올리니 대충 이해해 주시길. (via http://www.vlsiip.com/vcs/)(via http://salinasv.blogspot.kr/2011/05/simulating-mixed-language-hdl-using-vcs.html) VCS에 관한 간단한 사용법 소개. VCS is 3 step process 3단계로 구성된다.Compile/Analysis1차 간단한 문법 분석, vhdlan/vlogan 명..