IT/Cloud 2023. 5. 11.

MSA - 전환 계획 DB 분리 관련 참고 자료

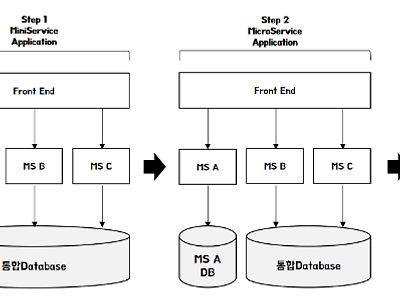

MSA 전환시에 고민되는 DB, 스키마 문제에 대한 선구자들이 많이 있다. 아래 글들을 꼭 읽어보고 정리해 보면 좋겠다. 마이크로서비스 아키텍처의 기준과 DB 분리 마이크로서비스 아키텍처의 기준과 DB 분리 개요 최근 3년 사이 마이크로서비스 아키텍처의 급격한 유행에 따라 많은 프로젝트에서 MSA로의 전환을 시도하고 있으며, 성공적으로 전환한 케이스가 있는 반면, 실패한 경우도 종종 발생하고 waspro.tistory.com 인상적인 그림이 있다. 전환시에 꼭 참고하자. MSA 전환 계획 DB 분리 관련 참고 자료를 정리해 드릴게요.😊 MSA 전환을 위해서는 서비스 별로 DB를 반드시 쪼개야 하는 것은 아니지만, 장기적인 관점에서 바라보았을 때 점진적 이행이 가능한 형태로 데이터베이스를 분리해 나가는 것..

IT/블로그 2020. 2. 7.

Hugo (휴고) 테마 적용 후 에러 발생시 대처한 내용

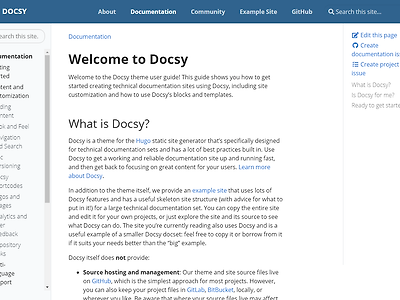

Hugo (휴고) 테마 적용 후 에러 발생시 대처한 내용 저장용으로 남겨두기 에러 내용은 아래와 같다. 적용한 테마는 docsy 라는 Google 에서 제공하고 있는 documentation 을 위한 테마이다. 막상 쓸 문서는 없는데, 시작한 거 데모는 돌려봐야지...흠 테마 홈페이지 : https://www.docsy.dev/ $ hugo --debug INFO 2020/02/07 18:43:51 No translation bundle found for default language "en" INFO 2020/02/07 18:43:51 Translation func for language no not found, use default. INFO 2020/02/07 18:43:51 i18n not ini..

IT/ASIC | FPGA 2019. 11. 18.

정전기 방전 손상모델및 시험방법 - ESD 반도체 테스트 자료

구글 검색 후 기술자료 모음 정전기 방전 손상모델및 시험방법정전기 방전 손상모델및 시험방법 - ESD 반도체 테스트 자료 전파기술원 2011.03 뉴스레터 자료 중 발췌된 내용 LG전자 정전기 교육 자료 2001 년도 자료로 연식이 좀 되었는데, 이쪽 기술이 고만고만해요.. 왜 발전이 느린지 회로내의 과전압,과전류(Surge)로 인한 IC 파괴 대부분의 IC불량 유형임 기타 기사들 그리고, 검색된 좋은 기사도 여기에 저장. [SMT와 ESD 제어 기술 4] EOS/ESD 불량 분석, 이렇게 해결하라 [SMT와 ESD 제어 기술 4] EOS/ESD 불량 분석, 이렇게 해결하라 [SMT와 ESD 제어 기술 4] EOS/ESD 불량 분석, 이렇게 해결하라 www.hellot.net

IT/IoT | Hardware 2019. 1. 11.

스마트폰으로 간단하게 Arduino 제어하기 (3) - Remote Display

스마트폰으로 간단하게 Arduino 제어하기 (3) - Remote Display 아주 쉬운 OLED 모듈을 이더넷 쉴드와 함께 연결하여 스마트폰으로 간단히 메시지를 보내서 출력하는 예제를 만들어 보았다. 기존의 LED 제어하는 것은 아래 글을 참고하세요. 스마트폰으로 간단하게 Arduino 제어하기 (1) - 아두이노 이더넷 (https://ts.devbj.com/568)스마트폰으로 간단하게 Arduino 제어하기 (2) - 어플 소개 (https://ts.devbj.com/570) 일단 결과는 아래 그림과 같다. 소스코드는 아래 gist 사이트에 올려 두었으니 참고하면 된다. LED 제어하기 예제에 OLED I2c Display library를 추가해서 간단하게 구현이 가능하다. https://gis..

IT/IoT | Hardware 2019. 1. 9.

IPv6 Cheat Sheet - 간략한구조 설명자료

IPv6 Cheat Sheet - 간략한구조 설명자료 http://ipv6.co.hu/wp-content/uploads/2012/04/IPv6-Cheat-Sheet.pdfhttp://www.roesen.org/files/ipv6_cheat_sheet.pdfIPv6 Header cheat sheet (src : http://packetlife.net/media/library/8/IPv6.pdf)대충 이렇게 생긴 자료입니다. 아래그림 참고

IT/IoT | Hardware 2019. 1. 9.

ICMPv6 메시지 정리테이블과 기술자료

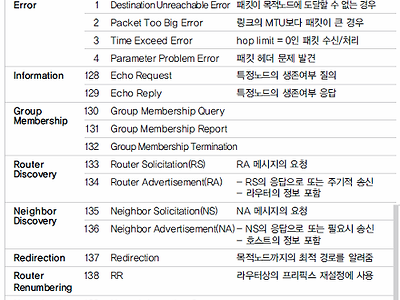

ICMPv6 메시지 정리테이블과 기술자료 (발췌 : 한국인터넷진흥원 『IPv6 보안 기술 안내서』). ICMPv6 처리와 관련된 좋은 자료..Managing an IPv6 Network: Deep Dive into ICMPv6 – Laura Knapp, AES (localcopy) 기타 다른 많은 좋은 자료도 많이 있다. 여기를 눌러서 살펴보자.http://rmv6tf.org/na-ipv6-summit/2013-na-ipv6-summit/2013-presentations 무튼 자료를 살펴보면, IPv6 Network Host의 경우 관리해야 할 정보들이 많다. (즉, 이걸 구현하려면 복잡해 져야 한다는 ㅜㅜ) Each host is to maintain the following:Neighbor Cache..

IT/ASIC | FPGA 2017. 7. 18.

ASIC, SoC, 반도체, 설계 관련 글 모음

ASIC, SoC, 반도체, 설계 관련 글 모음 여러군데, 혹은 여기에 단편적으로 적어두다 보니 목차같은 페이지가 없다. 좀 정리가 안되더라도 한 페이지에 모아서 저장해 두면 좋겠다 생각하던 차에 Github pages 를 이용하여 jekyll 블로그를 하나 만들어서 해당 페이지를 만들어 두었다. 업데이트 열심히 해야지 ASIC, SoC, 반도체, 설계 관련 글 모음 (http://devbj.com/asic/) ASIC ASIC Design Tutorials - 위키사이트, 전체흐름을 살펴보자. 설계, FPGA, 검증. HDL 설계에 사용되는 hdl 언어(VHDL, Verilog, SystemVerilog, …) 관련 자료를 모아두자. Verilog http://www.testbench.in/ - 테스트..

IT/ASIC | FPGA 2017. 5. 31.

[전자 기초] MOSFET의 원리

[전자 기초] MOSFET의 원리 트랜지스터 원리, 알고보면 간단해요^^ 트랜지스터 원리, 알고보면 간단해요^^ | 삼성디스플레이 뉴스룸 우리가 사용하고 있는 스마트폰, 태블릿PC, 데스크탑PC 등 셀수 없이 많은 전자 기기에 반도체가 들어가죠? news.samsungdisplay.com 중요한 것만 캡쳐. 원본글로 들어가서 보세요 자세한 것은 만화로 쉽게 이해하는 모스펫(MOSFET)의 스위칭 동작 원리 만화로 쉽게 이해하는 모스펫(MOSFET)의 스위칭 동작 원리 중학교 과학시간에 배운 전자회로에서 전압이 조금 걸리면 전류도 조금 흐르고, 전압이 많이 걸리면 전류도 많이 걸린다는 점을 기억하시나요? 즉, 전압이 걸린 이상 전류를 흐르지 않게 할 수는 없다는 말인데요.. blog.skhynix.com ..

IT/ASIC | FPGA 2017. 5. 26.

Temperature inversion

Temperature inversion – concept and phenomenon(http://vlsiuniverse.blogspot.kr/2015/04/temperature-inversion-deep-dive-into.html)머 공정이 낮아질수록 변수가 복잡해짐.단순히 온도가 낮고 높은 온도이면 best case 인데. 잘은 모르지만 공정이 낮아지면 원칙에서 벗어나 온도가 높아도 가끔 best case의 범위를 넘는 것들이 나오는 경우도 있음. 당연히 그 반대의 경우도 생각해야 하고...단어만으로 이해하면 이런 뜻이것 같은데. 머 틀려도 어쩔수 없지.시원한 바다가 생각나는 여름이~~출처: https://pixabay.com/en/santorini-oia-greece-water-1571484/

IT/ASIC | FPGA 2016. 7. 19.

Design compiler 관련 글 - Synopsys 합성 툴

Design compiler 관련 글 - Synopsys 합성 툴여기 저기 참 많이 있겠지만, 몇몇개 찾아서 본 자료들만 링크라도 모아 RTL 합성에 관련된 기본적인 내용이 잘 정리되어 있다. 아래 2개의 글만 숙지해도 문제가 없을 듯.Synthesis ABCs Part 1 - http://docslide.us/documents/syn-abc-part1.htmlSynthesis ABCs Part 2 - http://docslide.us/documents/syn-abc-part2.html그리고, 어렵게 찾아두는 한글 자료들. 열심히 하신 분들이 많이 계시네요. Design Compiler 정리 (http://blog.naver.com/PostList.nhn?blogId=beahey&from=postList..

IT/IoT | Hardware 2016. 4. 15.

이더넷 설명자료 - Ethernet Theory of Operation

이더넷 설명자료 - Ethernet Theory of Operation 마이크로 칩에서 올려둔 Application note 에서 발견엄청나게 잘 정리된 자료이다.이더넷 칩을 쓴다면 한번 꼭 읽어서 습득해 보자. http://ww1.microchip.com/downloads/jp/AppNotes/jp533903.pdf 혹시 몰라, 오프라인 버전으로 저장 기술적 내용이지만 재미없어도 꾹 참고 읽으면 복이온다 ^^짤방은 여기서 https://www.youtube.com/watch?v=8qTS2BiRZzU 갈무리한

IT 2012. 4. 17.

set_false_path / set_case_analysis

머 간단하게 정리하면,set_false_path means that particular path will not be considered for timing analysis. 즉 "타이밍 체크를 하지말아라" 라고 알려주는 구문,대부분, reset path 와 clock path 에 쓰여진다.그리고 multi clock을 사용하는 곳에서는 각 clock들 사이의 신호 교환 부분은 대부분 false path로 지정해야 한다.(아마, 설계에 sync logic은 들어가 있을 것으로 확신 ^^) source from http://lib.dicder.com/synthesis/2010/0615/228.html A false path can also be a path cross asynchronous clock do..