IT/ASIC | FPGA 2017. 5. 31.

[전자 기초] MOSFET의 원리

[전자 기초] MOSFET의 원리 트랜지스터 원리, 알고보면 간단해요^^ 트랜지스터 원리, 알고보면 간단해요^^ | 삼성디스플레이 뉴스룸 우리가 사용하고 있는 스마트폰, 태블릿PC, 데스크탑PC 등 셀수 없이 많은 전자 기기에 반도체가 들어가죠? news.samsungdisplay.com 중요한 것만 캡쳐. 원본글로 들어가서 보세요 자세한 것은 만화로 쉽게 이해하는 모스펫(MOSFET)의 스위칭 동작 원리 만화로 쉽게 이해하는 모스펫(MOSFET)의 스위칭 동작 원리 중학교 과학시간에 배운 전자회로에서 전압이 조금 걸리면 전류도 조금 흐르고, 전압이 많이 걸리면 전류도 많이 걸린다는 점을 기억하시나요? 즉, 전압이 걸린 이상 전류를 흐르지 않게 할 수는 없다는 말인데요.. blog.skhynix.com ..

Life/Private 2017. 5. 27.

구덕운동장

보인다. 날씨도 좋고. 다만 맘이 무거울뿐 ㅎ 다들 힘내쟈 ^~^

IT/ASIC | FPGA 2017. 5. 26.

인터뷰 예상 질문 - 반도체 설계 인력

이런 대단한 블로거가 있나? 반도체 설계자들이 인터뷰 준비를 위한 예상 질문리스트 (답변은 일부 있음) 정리해 놓은 글 발견세세히 다 알지는 못하지만 자기 분야에 맞는 글을 읽어보고 정리해 보면 쵝오~~Backend (Physical Design) Interview Questions and AnswersMar 12, 2008 ... Backend (Physical Design) Interview Questions and Answers. Below are the sequence of questions asked for a physical design engineer.asic-soc.blogspot.com/2008/.../backend-physical-design-interview.htmlCompanywis..

IT/ASIC | FPGA 2017. 5. 26.

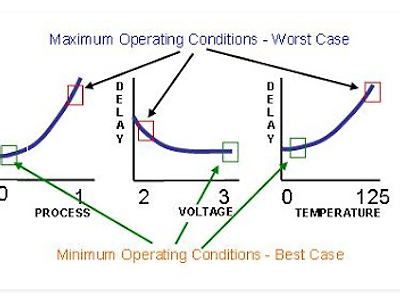

Temperature inversion

Temperature inversion – concept and phenomenon(http://vlsiuniverse.blogspot.kr/2015/04/temperature-inversion-deep-dive-into.html)머 공정이 낮아질수록 변수가 복잡해짐.단순히 온도가 낮고 높은 온도이면 best case 인데. 잘은 모르지만 공정이 낮아지면 원칙에서 벗어나 온도가 높아도 가끔 best case의 범위를 넘는 것들이 나오는 경우도 있음. 당연히 그 반대의 경우도 생각해야 하고...단어만으로 이해하면 이런 뜻이것 같은데. 머 틀려도 어쩔수 없지.시원한 바다가 생각나는 여름이~~출처: https://pixabay.com/en/santorini-oia-greece-water-1571484/

IT/ASIC | FPGA 2017. 5. 26.

Process-Voltage-Temperature (PVT) Variations and Static Timing Analysis

참고글 소개, 너무 기술적인 내용이라 읽기는 싫지만 가끔은 찾아봐야 함(http://asic-soc.blogspot.kr/2008/03/process-variations-and-static-timing.html)Sources of variation can be:Process variation (P)Supply voltage (V)Operating Temperature (T)The best and worst design corners are defined as follows:Best case: fast process, highest voltage and lowest temperature 빠른 공정, 높은 전압, 낮은 온도Worst case: slow process, lowest voltage and hig..

IT/ASIC | FPGA 2017. 5. 25.

[전자] EOS / ESD - 기초 지식

관련글 링크 2016/02/26 - [IT/ASIC | FPGA] - [반도체] ESD Test - HBM,MM,CDM 자료 모음 2017/07/18 - [IT/ASIC | FPGA] - ASIC, SoC, 반도체, 설계 관련 글 모음 EOS 와 ESD 에 대한 기초지식 네이버 블로그 검색으로 해결~ http://blog.naver.com/bkpark777/80164645562 ESD에 대해서 서지 (surge)와 ESD의 차이점이 뭔가요? ESD는 Electrostatic Discharge 의 약자로서 정전기를 방... blog.naver.com EOS(electriocal overstress : 전기적 과부하)의 일반 용어로 볼 수 있고, EOS는 번개(lightning), 전기자기파(EMP), 정전..

IT/ASIC | FPGA 2017. 5. 25.

[Tool] ANSYS PathFinder

ESD / EOS 관련 이야기가 막 나오니깐..패쓰파인더라는 툴이야기가 나오네. ESD는 기존의 관련 글 참고 : ESD Test - HBM,MM,CDM (http://ts.devbj.com/425)ANSYS (자회사 Apache) 에서 나오는 Pathfinder . 정보는 일단 간단한 코멘트와 저장을 해 두어야 나중에 가치가.https://www.apache-da.com/products/pathfinderANSYS PathFinder is an electrostatic discharge (ESD) planning, verification and sign-off solution for full-chip SoC and IP designs. It is applied in layout and circuit-l..