IT/ASIC | FPGA 2024. 2. 20.

Verilog - Parameter, deparam 사용법

모듈내에 데이터 비트등을 선언할때 정의를 하도록 하려면 Parameter 방법을 이용해야 한다. Hard-fix 코드로 박아두면 항상 문제가 생기곤 했다. 귀찮아도 꼭 미리 해두자 Parameter 선언 인스턴스 생성시에 데이터 비트를 지정하게 하는 방법은 모듈을 만들때 아래처럼 파라메터 값을 받아 처리하도록 하는 것이다. C/C++ 코드의 생성자 함수내의 파라메터를 같은 개념이지 module #() ; 아래 예제는 여기서 가져왔다. https://docs.xilinx.com/r/en-US/ug901-vivado-synthesis/Parameters-Example-Verilog module myreg (clk, clken, d, q); parameter SIZE = 1; input clk, clken; ..

IT/ASIC | FPGA 2024. 2. 16.

Verilog - 합성에 유리한 coding 스타일

HDL(Verilog, VHDL, ...) 머든 실제 합성이 설계한 대로 되지 않으면 완전 무용지물이다. 코딩때 부터 신경써야 하는데, 많이 까먹었네. 따로 정리한 문서를 찾아보자. 일단 아래글을 찾아와서, 정리해보자. (지금 정리중...읽고 내 생각 넣고 머 이렇게) 예제나 설명에 대한 자세한 내용은 아래 해당 블로그 님의 글을 방문해서 보심이 맞는것 같습니다. https://trts1004.tistory.com/12108949 일단은 제 개인 공부용으로 복사해서 정리중.... 추가로 자료가 하나더 있다. 엄청 기본적인것인데 5분이면 읽어본다. 함 읽어보자. 1. 블록도를 그려라, 라벨을 붙이고, 시그널 적고, width 명기하자. 2. 타이밍도를 그려라 최대한 자세하게 3. 합성 가능한 코드 템플릿(..

IT/ASIC | FPGA 2024. 2. 15.

Verilog - 파이썬으로 테스트 벤치 작성하기 cocotb - 킵

파이썬으로 테스트벤치를 작성하도록 도와주는 파이썬 프로젝트가 있어 일단 킵 이름은 cocotb 라고 하네 공식 사이트는 여기 https://docs.cocotb.org/en/stable/index.html cocotb cocotb is a COroutine based COsimulation TestBench environment for verifying VHDL and SystemVerilog RTL using Python. 일단 지원되는 시뮬레이터 종류는 다음과 같다. cocotb 기본 골격 A typical cocotb testbench requires no additional HDL code. The DUT is instantiated as the toplevel in the simulator wi..

IT/ASIC | FPGA 2024. 2. 15.

Verilog 기초 - case 문

Verilog 기초 문법과 관련된 것도 하나씩 정리해 보자. 오늘은 case 문이다. if 문과는 다르게 병력적으로 우선순위 없이 생긴다는 장점이 있다. 반드시 우선순위가 필요하다면 if else 문을 사용해야 하며, 같은 조건에서 mux 하는 로직 같은 경우에는 case 문을 활용하면 된다. 아래 문법과 예제는 다음 사이트에서 참고하였다. https://vlsiverify.com/verilog/case-statement/ Case 문법 기본 문법은 다음과 같다. case() : : : : begin ... ... end default: endcase 사실 예제로 보는 게 가장 낫다. Case 예제 module case_example; reg [2:0] data; always @(data) begin c..

IT/ASIC | FPGA 2024. 2. 13.

Xilinx Vivado - 다운로드 및 설치

FPGA 에 프로그래밍 할 수 있는 툴인 Vivado를 다운로드 하고 설치해 보자. 사용자 계정 생성 우선 툴 제공 업체인 AMD 사이트에서 계정을 먼자 만들고 로그인 해야 한다. 계정 생성하는 방법은 AMD 사이트에서 로그인 버튼은 누르면, 아래와 같이 생성할 수 있는 "계정 만들기" 버튼을 볼 수 있다. 클릭해서 생성작업을 해보자. 정보를 입력하고 생성이 완료되면, 꼭 로그인을 하도록 한다. Vivado Download 이제 Vivado 툴을 다운로드 하면 된다. 해당 툴을 다운로드 하는 경로는 아래와 같다. 다운로드 주소https://www.xilinx.com/support/download/index.html/content/xilinx/en/downloadNav/vivado-design-tool..

IT/ASIC | FPGA 2024. 2. 5.

Verilog - flatten array - 2차원 배열 1차원으로 변환

Verilog 에서 포트로 넘길때 2차원 배열이 되지 않는다는 슬픈 진실이 있네 ㅜㅜ 일단 보통 합성할 때 합성툴에서 다 자동으로 해줄 듯 한데 이를 손으로 해야 한다니 일단 방법은 알아두자고 https://stackoverflow.com/questions/28623819/how-to-flatten-array-in-verilog How to flatten array in Verilog As Verilog does not allow to pass the array as input to module, so how can we flatten any array in Verilog. Suppose I have this array: parameter [31:0] A [0:31]; wire [31:0] B I wan..

IT/ASIC | FPGA 2024. 1. 25.

Xilinx JTAG – HS2, HS3, Platform Cable USB II

Xilinx JTAG 케이블 종류가 많은데 숫자가 보통 높은걸로 선택하는데 이것은 JTAG HS2 가 호환성이 더 좋은듯 Digilent FPGA 보드를 많이 쓰니, 해당 회사에서 만든 제품으로 알아보자!! https://digilent.com/reference/programmers/jtag-hs2/reference-manual?_ga=2.209894997.1913691520.1700123539-2102363698.1698815413#supported_target_devices Is JTAG-HS2 is compatible with Artix 7 series FPGA? @vertika.s, Yes, it is compatible. You can view the full supported Artix 7 시..

IT/ASIC | FPGA 2019. 4. 25.

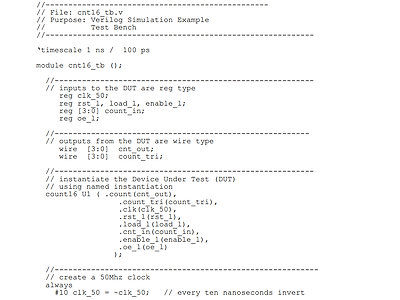

[HDL] Test Bench 작성가이드 in Verilog

이것저것, 책도 인터넷도 뒤져봐도 기본이 중요 첨부된 자료정도면 기본 이해 뿐 아니라 왠만한 건 그냥 해결 가능 카운터 테스트를 예제로 해서 자세히 설명되어 있음. 반드시 숙지한 후 작업에 적용하기 원본 소스 : http://people.ece.cornell.edu/land/courses/ece5760/Verilog/LatticeTestbenchPrimer.pdf 꼴랑 10페이지니깐, 다 외울 수도 있겠다. 모듈 인스턴스 정의하고, 맵핑하고, 클럭 정의해서 기본으로 주는 부분. 추가로 디버깅을 위해 출력하는 예제 부분만 살짝 캡처 초초 기본이니깐 너무 큰 기대는 말고, 다들 짜요~~

IT/ASIC | FPGA 2016. 9. 22.

edge detect pulse - 트리거된 이벤트를 알아내 한 클럭 pulse 만들기

머 제목부터 어렵다.정하기가..국어가... 왜 - 시나리오어떤 신호가 '1' 인 상태로 여러 클럭에 걸쳐져 있다.그런데 나는 '0' 에서 '1'로 올라간 이벤트를 알려주는 것처럼 한 번의 사건에 한 클럭만큼의 이벤트 펄스를 만들기를 원한다.해결은 그림으로이렇게 하면 된다. 즉 그림의 OUT 신호를 보고 사용하면 해결~~그림은 남이 그린 것이므로 원본글의 위치를 알려드립니다.보시고 HDL 코드도 필요하다고 생각하시면 해당글에 가셔서 꼭 읽어보세요. http://www.boldport.com/blog/2015/4/3/edge-detect-ad-nauseam 즐~~

IT/ASIC | FPGA 2016. 9. 22.

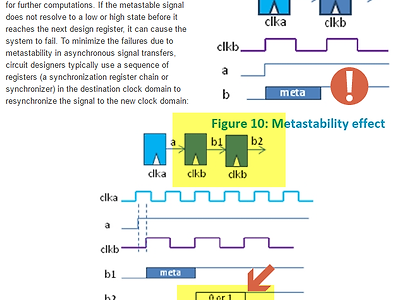

CDC(Clock Domain Crossing) 설계시 반드시 들어가는 synchronizer

이전글에 이어 하나더, ASIC 설계시에 가장 중요한,실제 합성 후의 이상한 현상이 발생하는 경우 가장 많이 의심하는 이부분 CDC 설계에서 기본적인 것이라 볼 수 있다.그림으로 설명이 가능하다.물론 원본글은 아래 글에 방문하여 전체를 읽어 보는 것이 좋다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 무작정 다른 클럭의 시그널을 보고 사용하는 경우 Meta 상태의 값을 레퍼런스 할 수 있으므로이후 동작을 보장할 수 없다. 경우에 따라 다른 상황이 발생할 수도 있고, 잘 동작할 수도 있다. 운좋게.. 무튼, 그래서 무조건 F/F 2개 정도를 clock domain 사이에 넣어주는 것이 일반적인 기법..

IT/ASIC | FPGA 2016. 9. 22.

Recommended reset synchronization scheme

설계시 참고할 내용이 정말 많은 필수 페이지 일단 그중에서 필요한 내용은 바로 이것.원본글은 여기다. https://electronicsnews.com.au/best-design-practices-for-high-capacity-fpga-devices/ 이 그림이 뜻하는 바는 알고 가자. 리셋상태로 가는 것은 언제든지 async 한 조건으로 가고리셋에서 풀리는 경우에는 내부 시스템 클럭에 맞추어서 풀리도록 한다.여러 F/F 동작에 안정성을 부여할 수 있다. 즐

IT/ASIC | FPGA 2015. 12. 29.

Simulating verilog VHDL using Synopsys VCS - 칩 설계 검증 툴

Synopsys VCS 사용 - HDL compile & simulation, 칩 설계 검증 아래 2가지 원본 글을 가지고 아래와 같이 간단한 tutorial을 만들어 보았다. 한글이 곳곳에 보이도록 했다. 그래도 원본을 감상하시는 예의를 갖추도록.정리는 하고 있는 중인데, 자료는 쓸만해서 그냥 올리니 대충 이해해 주시길. (via http://www.vlsiip.com/vcs/)(via http://salinasv.blogspot.kr/2011/05/simulating-mixed-language-hdl-using-vcs.html) VCS에 관한 간단한 사용법 소개. VCS is 3 step process 3단계로 구성된다.Compile/Analysis1차 간단한 문법 분석, vhdlan/vlogan 명..